PCIe 7.0 стал на шаг ближе к реальности — опубликованы полные предварительные спецификации стандарта

PCI Special Interest Group (PCI-SIG) опубликовала первую предварительную версию полных спецификаций стандарта PCIe 7.0 для рассмотрения участниками организации. Проект включает в себя все изменения спецификаций, которые PCIe 7.0 получит по сравнению с PCIe 6.0. Новая версия PCI Express по-прежнему готовится к полному выпуску в 2025 году.

Источник изображений: PCI-SIG

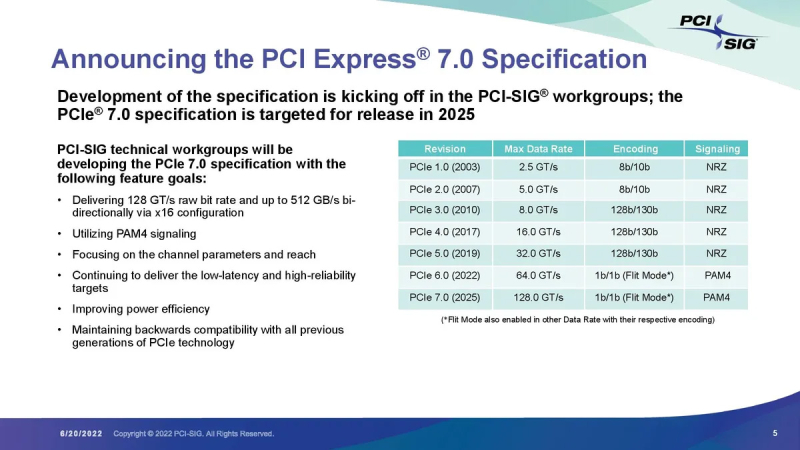

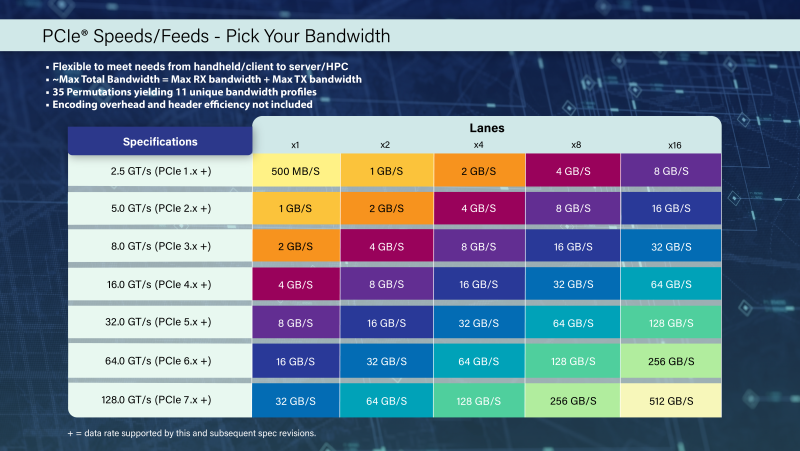

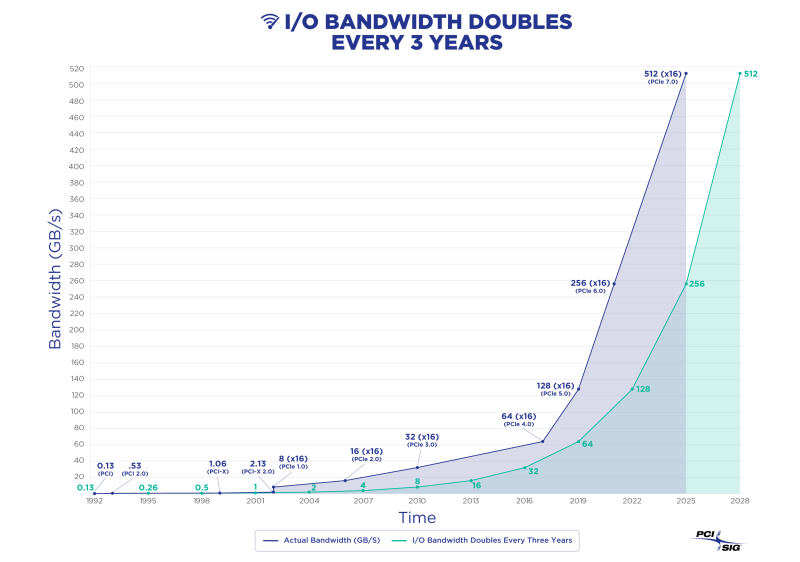

Стандарт PCIe 7.0 предложит пропускную способность до 128 ГТ/с (гигатрансферов в секунду), что вдвое больше, чем у PCIe 6.0. Это означает, что слот PCIe 7.0 x16 сможет обеспечить внушительную пропускную способность в 512 Гбайт/с от процессора к карте расширения и обратно.

Вместе с двукратным приростом пропускной способности по сравнению с предыдущим стандартом, в PCIe 7.0 будут использоваться некоторые технологии, которые применяются в PCIe 6.0, включая модуляцию PAM-4 и кодирование Flow Control Unit (FLIT) 1b/1b, позволяющее осуществлять прямое исправление ошибок (FEC) в передаваемых пакетах фиксированного размера. Это делает архитектуру PCIe 7.0 очень похожей на PCIe 6.0, что может ускорить её внедрение.

Переход от PCIe 4.0 к PCIe 5.0 удвоил скорость передачи данных за счёт увеличения частоты шины, что наложило свои ограничения, например, почти вдвое сократив допустимую длину электрических путей. Это означает, что устройства для передачи и приёма сигнала пришлось размещать ближе друг к другу, чтобы обеспечить целостность сигнала. Также это потребовало использования более толстого текстолита на основе более прочных и дорогих материалов в материнских платах.

Новый интерфейс PCIe 6.0 снова удвоил пропускную способность относительно PCIe 5.0, но это увеличение произошло за счёт применения кодирования PAM-4 с NRZ вместо увеличения частоты, поэтому требования PCIe 6.0 к длине электрических путей остаются примерно такими же, как у предыдущего стандарта. В то же время кодирование PAM-4 сильнее подвержено ошибкам, поэтому частота ошибок у PCIe 6.0 увеличилась, даже несмотря на добавление функции прямой коррекции ошибок (FEC). Это в свою очередь, сокращает показатель эффективной пропускной способности. Ретаймеры могут помочь решить эти проблемы, но их использование также увеличивает затраты.

На данный момент релиз окончательных спецификаций PCI Express 7.0 ожидается в 2025 году, а массовое появление продуктов на их основе запланировано на 2028 год. Впрочем, первые устройства с его поддержкой наверняка появятся чуть раньше. Тем не менее, распространение нового стандарта поначалу будет в основном ограничено рынком корпоративных и серверных устройств.