Процессор Cell: шаг в будущее

Стр.1 - Часть I

PowerPC "восстаёт из пепла"

Апрель 1993 года. Сформированный двумя годами ранее альянс Apple, IBM и Motorola объявил о выпуске первого процессора на базе революционной архитектуры PowerPC - PowerPC 610 с частотами 50 и 66 МГц. Новинка была призвана составить достойную конкуренцию чипу Pentium из мира x86. Эра PowerPC началась.

За PowerPC 610 последовали модели второго поколения с индексами 603/604, принёсшие с собой незначительные нововведения. В 1997 году появился PowerPC 750 (a.k.a. G3) - чип третьего поколения, отличавшийся от предшественников увеличенной частотой системной шины и встроенным L2-кэшем.

Выпуск 31 августа 1999 года компанией Motorola процессора PowerPC 7400 (G4) явил миру блок векторных вычислений AltiVec, позволивший зачислить компьютеры PowerMac G4 на его основе в ранг настольных суперкомпьютеров. Будущее PowerPC казалось "безоблачным".

Первые "подводные камни" появились во время мучительных попыток Motorola преодолеть гигагерцовый рубеж. Бросив идею дальнейшего развития PowerPC 74хх "под откос", компания сосредоточила все свои силы на процессоре PowerPC 8500 (первый G5).

Но, из-за задержек Motorola с выпуском больших партий годных чипов зародилось мнение о том, что архитектура PowerPC отжила свой недолгий век, а сам PowerPC 8500 стал "надгробным камнем" на "могиле" отдела компании по производству настольных процессоров.

Дальнейшее развитие архитектуре PowerPC дала IBM, разработав в 2002 году 64-разрядный процессор PowerPC 970 (G5). За ним последовал улучшенный PowerPC 970FX, а на горизонте уже "маячит" двуядерный PowerPC 970MP.

Не будем забывать и про чипы PowerPC 8641D (два процессора поколения G4 с 1 Mb L2-кэша на каждое ядро, встроенные контроллеры DDR2 RAM, PCI-Express, Gigabit Ethernet и RapidIO), разрабатываемые компанией Freescale.

Впрочем, архитектура всех этих чипов, как и x86, практически не изменилась со времён появления на рынке PowerPC 750/7400.

И вот, настал момент очередного скачка в развитии PowerPC, как качественного (в плане инноваций), так и количественного (в плане распространённости). Имя ему - архитектура Cell (от англ. "cell" - клетка, ячейка).

Когда?

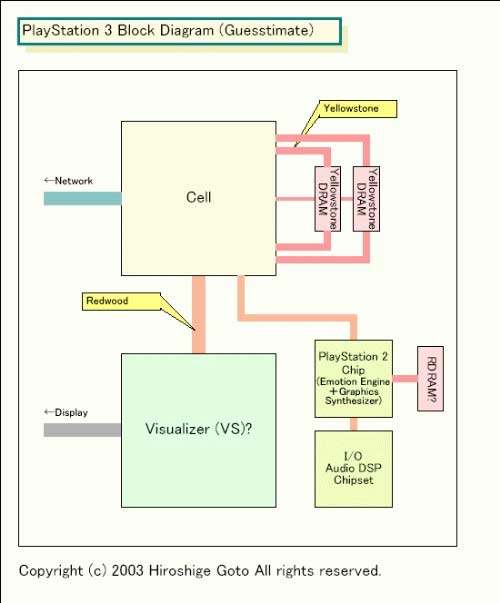

О своём намерении выйти на рынок графических рабочих станций с собственным процессором президент SCEI (Sony Computer Entertainment Inc.) Кен Кутараги (Ken Kutaragi) заявил в начале 2000 года. В то время компания собиралась начать массовые поставки чипа Emotion Engine, являвшегося ЦП для игровой консоли PlayStation 2 (и изначально для неё разработанного). К сожалению, трудности Sony с производством процессора, сложность его программирования, и, самое главное, отсутствие сильных партнёров не позволили осуществиться мечтам Кутараги.

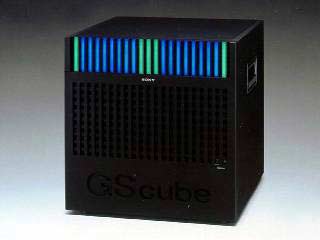

Хотя кое-чего компания всё-таки смогла достичь. Вспомним про GScube, разработанный самой SCEI и представленный публике на конференции Siggraph 2000.

Данная, хм, рабочая станция состояла из 16 связок чипов Emotion Engine и Graphics Synthesizer (PlayStation 2), объединённых в единую параллельную систему, оснащённую 2Gb оперативной и 512Mb видеопамяти.

GScube изначально предназначался в качестве отработки навыков в создании игр для PlayStation 3 (уже тогда будоражившей умы учёных SCEI), но, способный обрабатывать 1,15 млрд. полигонов в секунду (при HDTV-разрешении 1920x1080 пикселей), был принят на вооружение в качестве "визуализатора". Созданные студиями Square Pictures (фильм "Последняя фантазия: духи внутри нас") и Manex Visual Effects (компьютерная графика в фильме "Матрица") демки поражали своей сложностью и фотореалистичностью. Тем не менее, из-за того, что GScube не был самодостаточным и требовал для своей работы сервер SGI Origin 3400, купить его могли себе позволить немногие.

Впоследствии SCEI увеличивала количество связок чипов с 16 до 64, но рынок оставался по прежнему "холоден". GScube не прижился. Тем не менее, компания не потеряла надежду стать "Intel в лагере PowerPC", и, заручившись поддержкой корпораций Toshiba, IBM и своей "мамы" Sony (сформировавшийся альянс получил название STI), приступила к созданию архитектуры Cell.

Впервые описание работы процессора стало доступно после регистрации 22 марта 2001 года патента № 6809734 и заявки на патент № 20020138637 . Автором патента значился Сузуоки Масаказу (Suzuoki Masakazu), глава процессорного подразделения SCEI и разработчик Emotion Engine. Со временем в прессу стали просачиваться всё новые подробности относительно Cell, а 7 февраля на конференции ISSCC 2005 (International Solid State Circuits Conference) IBM, Toshiba и SCEI рассказали публике об архитектуре чипа, его применении, и своих будущих планах. Благодаря этому, на сегодняшний день можно более менее чётко обрисовать картину того, что же нас ждёт в конце 2005 - начале 2006 года.

Философия Cell

Принципы, заложенные в архитектуру нового чипа, были разработаны в начале 2000 года инженерами IBM. Идея массового параллелизма, на основе которой работает Cell, была заложена в так называемую ("cellular architecture") "клеточную архитектуру", в которой для создания суперкомпьютеров используется множество однотипных процессоров (от 10 тыс. до 1 миллиона), каждый из которых оснащён собственным контроллером RAM и определённым объёмом самой оперативной памяти.

Стоит также вспомнить про Beowolf-кластеры, построенные на базе простых компьютеров-"кирпичиков" и объединённые в единую систему.

В 2001 году во время обнародования первых данных Кен Кутараги сопоставил Cell с построенным по принципу кластерной системы суперкомпьютером Deep Blue. Сравнение было дано не просто так: оно отображает саму философию Cell. "Благодаря встроенной возможности объединения чипов Cell, микропроцессоры, являющиеся сегодня "индивидуальными островками", будут связаны между собой более тесно, благодаря чему сеть на основе таких процессоров превратится в одну унифицированную "суперсистему".

Как простые биологические клетки в теле, объединяющиеся для создания полноценных физических систем, электронные устройства на базе Cell будут блоками для больших систем", - так описывал Кутараги концепцию Cell.

Что же значат его слова? Cell может работать не только в качестве, собственно, процессора, но и в качестве элемента большой системы. Путём объединения различной техники, содержащей чипы Cell, можно построить единую сеть, которая будет функционировать, как одно "устройство". Представим следующую ситуацию: консоль PlayStation 3 подключена к HDTV-телевизору, к которому, в свою очередь, подключён Blu-Ray-рекордер. Все три устройства оснащены процессорами Cell. Пользователь, играя в какой-нибудь WipeOut Fusion 2, даёт команду рекордеру записать очередной заезд в HDTV-формате. При этом Cell в телевизоре помогает своему "напарнику" записывать игру. После записи освободившиеся Cell'ы телевизора и рекордера "спешат на помощь" процессору PlayStation 3, в результате чего количество FPS в игре многократно ускоряется.

Таким образом, производительность отдельных Cell-устройств в сети может повышаться за счёт процессоров других устройств. Причём чипам безразлично, где находятся другие элементы сети: в одной комнате, доме, городе, или на другом континенте. Да и устройства, кстати, могут быть абсолютно разные: от уже упоминавшихся игровых консолей и телевизоров до персональных компьютеров, КПК и даже мобильных телефонов!

Единая глобальная сеть. Разве не об этом долгие годы мечтают писатели-фантасты? С приходом Cell мечты могут стать реальностью. Но мы отложим их на потом и перейдём к теме статьи - процессору Cell.

"Клетка"

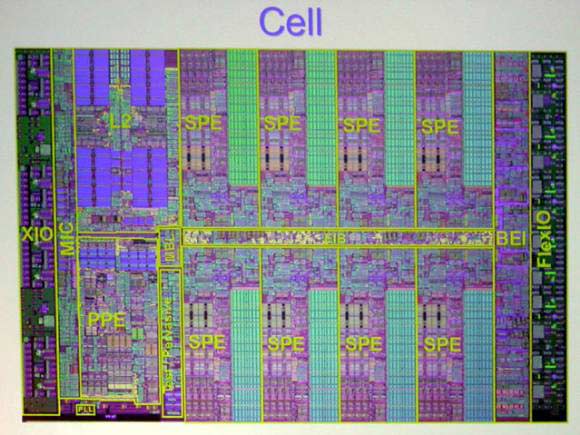

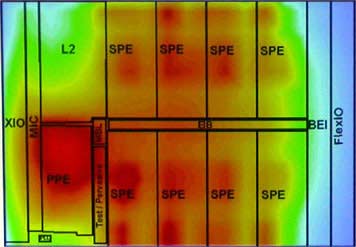

- Процессорного Элемента на основе POWER-архитектуры (PPE - POWER Processor Element);

- Восьми Синергических Процессорных Элементов (SPE - Synergistic Processor Element), ранее называвшихся Присоединяемыми Процессорными Устройствами (APU - Attached Processing Unit);

- Шины Взаимосвязываемых Элементов (EIB - Element Interconnect Bus);

- Контроллера Интерфейса Памяти (MIC - Memory Interface Controller);

- Контроллера Интерфейса Шины ввода/вывода (BIC - Bus Interface Controller).

Процессорный элемент на основе POWER-архитектуры

К сожалению, на ISSCC 2005 о PPE рассказывали меньше всего, поэтому такие важные характеристики процессорного ядра, как его архитектура и производительность остались "за кадром". Тем не менее, кое-какие данные нам уже известны.

PPE представляет собой два 64-разрядных процессорных ядра (на основе POWER-архитектуры) с поочерёдным выполнением команд (in-order execution), в отличие от внеочередного выполнения (out-of-order execution), присущего всем современным процессорам. PPE поддерживает технологию одновременной обработки двух потоков (SMT - Simultaneous Multi-Threading), примерным аналогом которой является Hyper-Threading в Pentium 4. В PPE присутствует блок VMX (VMX - Vector Multimedia eXtensions, более известный как AltiVec). Объём кэша L1 составляет 64 Kb (по 32 Kb на кэш инструкций и данных), L2-кэша - 512 Kb. Несмотря на сравнительно небольшой 11-стадийный конвейер PPE, представители STI заверяют, что запас по наращиванию частоты у Cell очень большой.

Стоит сказать пару слов об архитектуре PPE. Из-за отсутствия информации многие стали гадать, какой же процессор будет положен в её основу. Большинство "за" упрощённый POWER 5, часть отдаёт "предпочтение" PowerPC 970. Но оба варианта вызывают явные сомнения. Оспаривая их достоинства и недостатки, люди забывают, что разработка POWER 5 и PowerPC 970 велась в 2000-2004 годах, и они не были готовы к 2000 году, когда были начаты работы над Cell. Более вероятно следующее.

В конце прошлого столетия IBM решила создать процессор, работающий на сверхвысоких, как для того времени, частотах. В результате исследований в 1998 году в журнале Journal of Solid State Circuits (JSSC) был описана реализация чипа, основанного на части инструкций POWER-архитектуры. В 2000 году на конференции ISSCC 2000 стал доступен пресс-релиз, описывающий процессор на основе "полной" POWER-архитектуры, работающий на частоте 1 GHz (13-стадийный конвейер, тех. процесс 0,25 мкм). В дальнейшем прототип был переделан в сторону увеличения частоты (уменьшен конвейер) и уменьшения тепловыделения (улучшенный тех. процесс и применение всех современных технологий при производстве). Кроме того, были добавлены SMT и блок VMX. В результате получился PPE. Но "гадание на кофейной гуще" - не наша задача, поэтому давайте перейдём к SPE, благо о нём известно практически всё.

Синергический процессорный элемент

Синергический процессорный элемент представляет собой специализированный векторный процессор, обрабатывающий SIMD-инструкции (аналог SSE в Pentium и 3Dnow! в Athlon). Архитектура SPE довольно проста и напоминает процессоры эры PowerPC 601 и первых Pentium: четыре блока для работы с целочисленными векторными операциями и четыре блока для работы с числами с плавающей запятой. Правда, при этом большинство арифметических инструкций представляют собой 128-разрядные векторы, разделённые на четыре 32-битных элемента. Каждый SPE оснащён 128 регистрами, разрядность которых - 128-бит. Вместо кэша L1 процессор содержит 256 Kb собственной "локальной памяти" (local memory, также называемой local store) разделённой на четыре отдельных сегмента по 64 Кбайт каждый, а также DMA-контроллер. Последний предназначен для обмена данными между основной памятью (RAM) и локальной (LM/LS), минуя PPE.

Локальная память, по сути, выполняет роль кэша L1, но при этом полностью контролируется программистом, вследствие чего организована значительно проще. Достигается это путём переноса логики контроля за переполнением кэша из самого чипа в программный код, что способствует облегчению архитектуры локальной памяти (отсутствует поиск в RAM при каждом обращении к LM, упреждающая выборка и т.д.).

Благодаря наличию динамического механизма защиты памяти доступ к каждому SPE в Cell может быть закрыт, вследствие чего данные, обрабатывающиеся этим процессором, будут недоступны другим (например, в Cell другого устройства).

Несмотря на то, что SPE представляет собой векторный процессор, он не является аналогом VMX/AltiVec. Как уже говорилось, SPE - отдельный микропроцессор, выполняющий собственные команды, а VMX являются блоком (подмножеством команд), выполняемых PowerPC (G4/G5).

В результате всего вышеперечисленного можно сделать вывод, что SPE довольно похож на векторные блоки Emotion Engine: локальная память, четыре 32-битных векторных регистра, команды инициализации DMA и т.д. В принципе, в этом нет ничего особенного: Sony и Toshiba (которой, кстати, принадлежит большое количество патентов на векторные вычисления, полученные во время создания "медиапроцессоров" для цифровой техники в середине 90-х) работали над созданием Emotion Engine (равно как и Graphics Synthesizer), и часть архитектуры старого процессора легла в основу нового.

Для каких целей могут быть использованы SPE? Ответ на этот вопрос тянет на отдельную статью, так что ограничимся самым важным.

Одной из областей применения Cell аналитики считают рынок цифровых сигнальных процессоров (DSP - Digital Signal Processor), высокая скорость которых обусловлена многопоточным просчётом векторных инструкций. Восемь параллельно работающих SPE позволяют составить достойную конкуренцию специализированным DSP-процессорам. Установка PCI-E-платы с Cell в простой компьютер будет невероятной находкой для музыкантов и учёных.

Если использовать Cell для построения видеокарты (возможен и такой вариант), то SPE могут служить пиксельными шейдерами и будут использоваться для конвейера просчёта. Не смейтесь. Сама IBM во время ISSCC 2005 заявила, что считает Cell комбинацией процессора и графического чипа. Благодаря прямой связи между всеми SPE с помощью шины EIB (о которой мы поговорим чуть ниже), а также локальной памяти в их составе, существует возможность динамически переключать различные процессорные элементы на выполнение той или иной части конвейера просчёта.

Чтобы не быть многословными, перечислим возможности использования SPE через запятую: просчёт физических моделей, тесселяция поверхностей высшего порядка в полигональные модели, инверсная кинематика, скелетная анимация, обработка воксельных данных, анимация частиц, компрессия/декомпрессия видеоданных в формате MPEG4 "на лету", просчёт алгоритма ray-tracing "на лету", преобразование аудиоданных из одного формата в другой "на лету", обработка алгоритмов шифрования, искусственного интеллекта… это предложение можно продолжать очень долго, но мы остановимся и перейдём к следующему элементу архитектуры Cell.

Стр.2 - Часть II

Шина Взаимосвязываемых Элементов

Данная шина связывает в единую систему PPE, SPE, а также контроллеры MIC и BIC. Она представляет собой четыре концентрических кольца (шириной 128 бит на кольцо), проходящих через все элементы Cell. Для уменьшения возникающих шумов одна пара "колец" передаёт данные в одном направлении, а вторая - в обратном. Данные, проходящие из одного SPE в другой, используют установленные в них специальные буферы/повторители, обеспечивающие беспрерывное движение данных по шине. Передавая по 96 байт за цикл, EIB способна обрабатывать более 100 уникальных запросов.

Дизайн EIB был создан специально для возможности дальнейшего масштабирования Cell. Длина маршрута сигнала не изменяется в зависимости от количества SPE. Так как данные путешествуют от одного SPE к другому, увеличение их количества приводит лишь к увеличению латентности транспортировки данных от одного элемента Cell к другому.

В текущей версии архитектуры Cell шина EIB организована таким образом, что SPE устанавливаются лишь по горизонтальной оси. Благодаря этому существует возможность легко добавлять/убирать дополнительные SPE, доводя их общее количество до максимально возможного на том или ином производственном тех. процессе (с добавлением SPE увеличивается длина кристалла процессора, что видно на рисунке ниже).

PPE, SPE и EIB представляют собой основу архитектуры Cell, единое трио, работающее вместе. Кратко его и рассмотрим. Сразу напомним, что SPE - отдельный процессор с собственным ОЗУ, пусть и не такой продвинутый, как современные Pentium или PowerPC. Поэтому и выполняет SPE свои собственные инструкции. Синергический процессорный элемент является "подчинённым" POWER-процессора, выполняя те задачи, которые на него возложит PPE. Тем не менее, работают они параллельно.

Вместе с Cell на свет появляется термин "апулет" (APUlet), произошедший от старого названия SPE. Он представляет собой объединённый в единое целое код векторной программы и обрабатываемые ею данные.

При необходимости использования "подчинённого" процессора PPE направляет апулет по EIB в предназначенный для этого SPE, где тот выполняется. Затем обработанный SPE апулет отправляется либо в RAM (если они необходимы PPE), либо в локальную память векторного процессора, из которой они могут быть перенаправлены через EIB в следующий SPE одного и того же Cell-чипа (архитектура Cell позволяет SPE работать конвейерно - один за другим).

Контроллер Интерфейса Памяти

Для непрерывного обеспечения PPE и SPE данными необходима память с очень высокой пропускной способностью. Разрабатывая PlayStation 2, Sony и Toshiba учли способность компании Rambus создавать высокоскоростные интерфейсы и память, приняв решение использовать Direct RDRAM в консоли.

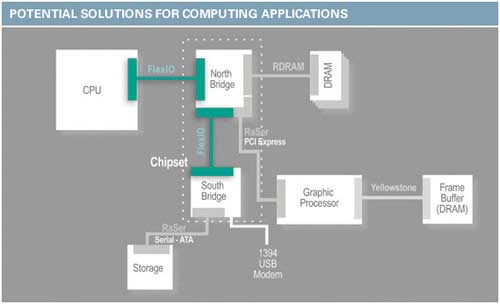

"Эксперимент" удался. И теперь, во время создания Cell, сотрудничество с компанией Rambus продолжается. Во время открытия ISSCC 2005 7 февраля президент компании Дэйв Муринг (Dave Mooring) объявил о лицензировании STI технологий памяти XDR RAM и высокоскоростной шины Flex I/O.

Двухканальная память XDR RAM (Ранее носившая кодовое название Yellowstone), используемая с Cell, обеспечивает суммарную пропускную способность в 25,2 Gb/sec. В подсистеме памяти каждый канал способен обслуживать до 36 чипов памяти, соединённых одними шинами команд (ШК) и данных (ШД). ШД каждого чипа подключается к контроллеру памяти через набор двунаправленных соединений типа "точка-точка". Сигналы передаются по ШК и ШД со скоростью 800 Мбит/с. Скорость передачи интерфейса "точка-точка" составляет 3,2 Гбит/с. При использовании устройств с разрядностью ШД 16 бит каждый канал XDR RAM может обеспечивать максимальную пропускную способность в 102,4 Гбит/с (умножаем 2 канала на 16-битную ШД и на проп. способность интерфейса "точка-точка" 3,2 Гбит/с) или 12,6 Gb/sec. Поэтому контроллер памяти текущей версии процессора Cell, использующего двухканальную память XDR RAM и 4 чипа памяти, обеспечивает пропускную способность в 25,2 Gb/sec.

К сожалению, чипы XDR RAM, в данный момент доступные на рынке, обладают ёмкостью лишь 512 Мбит, так что максимальный объём RAM в системе на базе Cell не может превышать 256 Мбайт. К счастью микросхемы памяти XDR RAM могут быть сконфигурированы таким образом, что 36 чипов будут подключены к одному 36-битному каналу. В такой конфигурации двухканальная XDR RAM может поддерживать до 32 Гбайт памяти (512 Мбит чипы) с коррекцией ошибок (ECC). Да-да, Дэйв Барски (Dave Bursky) из журнала Electronic Design Magazine заявляет, что подсистема XDR RAM использует 72 пары сигналов для ШД, что говорит о поддержке памятью ECC. Конечно, игровой консоли она не пригодится, но вот для рабочих станций и серверов будет, как говорится - "в самый раз".

Контроллер Интерфейса Шины ввода/вывода

Второй технологией, лицензированной STI, является интерфейс высокоскоростной шины Flex I/O (ранее носившей кодовое название Redwood), применённый в BIC. Flex I/O состоит из 12-байтных каналов (разрядностью 8 бит каждый). Шина использует 96 дифференцированных сигнальных пар для достижения пропускной способности в 6,4 Гбайт/с по одному каналу. Конфигурация канала асимметрична: 7 байт отводится на передачу, а 5 байт - на приём. Благодаря этому пропускная способность 12-битной пары составляет 44,8 Гбайт/с на передачу и 32 Гбайт/с на приём. В результате суммарная пропускная способность шины ввода/вывода составляет 76,8 Гбайт/с. Во Flex I/O реализованы две интересные технологии - FlexPhase и DRSL (Differential Rambus Signaling Level, дословно - дифференциальный уровень сигналов Rambus).

При размещении дорожек на печатной плате, инженерам необходимо соблюдать идентичность их длины (например, дорожки шины адреса Flex I/O). Благодаря этому сигналы, идущие по ним, будут приходить к приёмнику с одинаковой скоростью. Опоздание сигнала может привести к некорректной работе всей системы. Поэтому инженерам приходится закручивать дорожки в невероятные спирали, лишь бы сигналы по ним приходили в назначенное время.

FlexPhase представляет собой технологию выравнивания сигналов, приходящих не в заданное для них время. Достигается это путём задержки сигнала на приёмнике. Несмотря на возникающую латентность, такой приём позволяет намного упростить разводку печатной платы.

Вторая технология, DRSL, похожа на ту, что применяет корпорация Intel для уменьшения тепловыделения арифметико-логических устройств в своих Pentium 4. Не вдаваясь в технические подробности, объясним её так: при уменьшении напряжения питания устройства становится всё труднее отличать высокий уровень сигнала (или логическая "1") от низкого (логический "0"). Допустим, если 5В ещё можно отличить от 0В, то при величинах 0,09В и 0В сделать это намного труднее. Вместо поиска различий DRSL осуществляет "вычитание" напряжения двух величин и использует результат в качестве сигнального. Используя низковольтные сигнальные величины, можно свести тепловыделение к минимуму (даже несмотря на высокоскоростную шину).

Вполне возможно, что с распространением Cell и XDR RAM, и Flex I/O перекочуют в персональные компьютеры, дав компании Rambus второй шанс на этом рынке.

Общие сведения о Cell

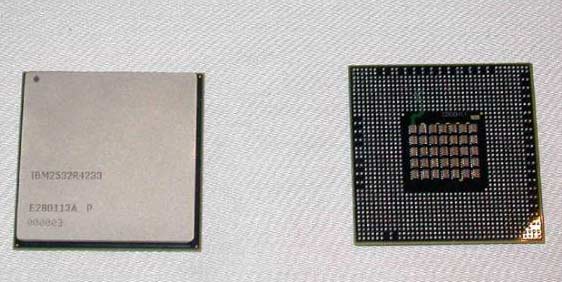

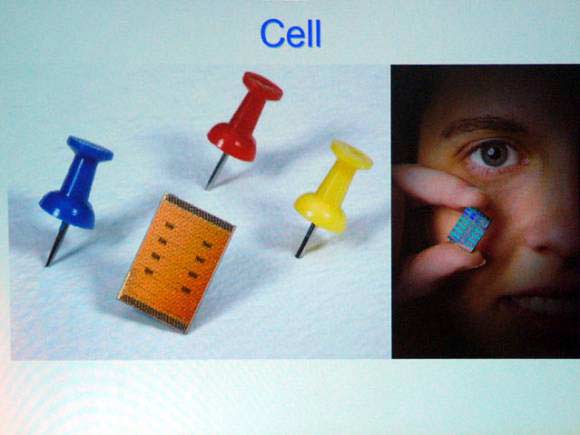

Разобравшись с архитектурой Cell, поговорим о его характеристиках. Продемонстрированный на ISSCC 2005 прототип процессора был изготовлен по 0,09 мкм тех. процессу (8-слоёв медных соединений) с использованием "кремния-на-изоляторе" (SOI, Silicon-on-Insulator). Количество транзисторов в чипе составляет 234 миллиона, площадь кристалла - 221 мм2 (приблизительно таким же был прототип Emotion Engine).

Каждый SPE в Cell состоит из 21 млн. транзисторов, из которых 14 млн. отводится на локальную память, а 7 млн. - на логику. При этом его размеры составляют 5,81 мм * 2,8 мм (0,09 мкм тех. процесс с применением SOI).

Кристалл Cell размещён внутри BGA-корпуса с размерами 42,5 * 42,5 мм. Из 1236 контактов процессора 506 являются сигнальными, а остальные предназначены для питания и "земли".

На ISSCC 2005 был продемонстрирован прототип, работающий на частоте 4 ГГц. При этом пиковая производительность восьми SPE, по заявлениям инженеров STI, составляет 250 Гигафлоп/с, или 250 миллиардов операций с числами с плавающей запятой (сравните это число с 851 Гигафлоп/с наименее быстрого суперкомпьютера из списка Top500). В лабораториях же STI "трудятся" Cell'ы с частотами от 3,2 до 5,3 ГГц (напряжение питания от 0,09В до 1,3В). Энергопотребление 5,3 ГГц чипа составляет около 180 Вт, 4 ГГц чипа - 80 Вт. При этом стоит учитывать, что эти процессоры - тестовые экземпляры, и изготовлены по "старой" технологии, которая при массовом производстве использоваться не будет.

Так, SCEI заявила, что процессор Cell, изготовленный по тех. процессу 0,065 мкм с использованием технологий SOI и "напряжённого кремния" (strained silicon) будет потреблять 30-40 Вт при частоте 4,6 ГГц. К тому же в Cell встроены один линейный и десять цифровых датчиков тепла, а также интеллектуальная система динамического понижения частоты процессора с пятью ступенями, позволяющая ещё более уменьшить тепловыделение и потребляемую мощность.

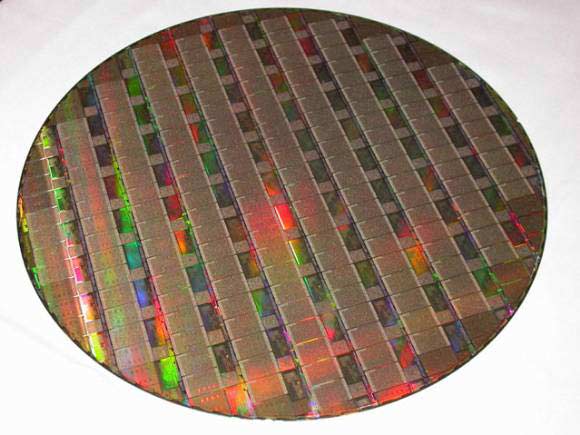

Начало массового производства Cell должно начаться в третьем квартале этого года. К тому времени завод IBM в Ист-Фишкилле (штат Нью-Йорк), построенный во времена 0,13 мкм тех. процесса, сможет производить 0,065 мкм пластины с кристаллами Cell. Завод же Sony в г. Нагасаки был изначально построен для Cell. Кроме того, IBM и Sony объявили о готовности вложить 2,5 млрд. долл в завод компании Infineon, строительство которого будет начато во второй половине этого года. Он поможет разгрузить производственные мощности партнёров и увеличить суммарный объём производства. IBM и Sony планируют выпускать вначале по 15 тыс. 30-мм пластин ежемесячно, постепенно увеличивая цифру.

Благодаря большим объёмам производства (десятки и сотни миллионов чипов в год) цена на процессоры Cell должна быть на приемлемом уровне. Желание STI конкурировать с Intel/AMD означает, прежде всего, ценовую войну. Даже после запуска в производство первых чипов Cell разработка архитектуры будет продолжаться. К 2010 году частоту процессоров, благодаря использованию всё более совершенного тех. процесса, а также оптических соединений между транзисторами, планируется поднять до 10 ГГц.

Cell в каждый дом!

Для какой же техники предназначен Cell?

Ещё 29 ноября прошлого года IBM, Sony Corporation и SCEI объявили о создании первой рабочей станции на базе прототипов процессора. Через некоторое время такие станции начали поставлять разработчикам "стартовых" игр для консоли PlayStation 3.

"Рабочая станция на базе Cell полностью изменит среду создания цифрового контента", - заявил Масаюки Чатани (Masayuki Chatani), технический директор (CTO) SCEI, - "Её невероятная мощь будет проявлять себя в разработке всех видов цифрового контента, начиная с фильмов и програм широковещательного ТВ, и заканчивая играми нового поколения для PlayStation".

Именно так. Рабочие станции на базе Cell предназначены не только для создания консольных игр. Они должны найти применение во всех областях, требующих больших вычислительных возможностей, таких как: видеомонтаж, создание компьютерных спецэффектов, научные расчёты и моделирование, большие базы данных, CAD-системы. Но не рабочие станции являются основным применением Cell. Главный продукт, для которого он разработан - PlayStation 3.

Прибыль, получаемая SCEI от PlayStation 2, составляет до 60% от общего дохода Sony (10% дохода компании, 3,59 мрд. долл. уходит на полупроводниковый бизнес ежегодно), так что компания старается из всех сил, чтобы консоль нового поколения получилась революционной. Судя по имеющейся информации, SCEI движется в правильном направлении. Судите сами: PlayStation 3 будет оснащена четырьмя чипами Cell с частотой 4,6 ГГц (пиковая производительность 32 SPE - 1 Терафлоп! И это не считая четырёх PPE и их блоков VMX!). Благодаря использованию четырёх процессоров пропускная способность подсистемы памяти составит 100 Гбайт/с. Правда, по имеющимся данным, объём XDR RAM составит "всего" 256 Мбайт, но будем надеяться, что компании, создающие игры, будут использовать эту память "с умом" (вспомним о 32 Мбайтах RAM, установленных в PlayStation 2, и о качестве игр для неё). Каждая консоль будет обладать портом интерфейса Flex I/O, благодаря чему подключать к ней аналогичные PlayStation 3 и другие устройства, оснащённые Cell, не составит особого труда.

Как уже сообщалось на 3Dnews, SCEI намерена продемонстрировать рабочий прототип PlayStation 3 до начала выставки E3 2005, что говорит о желании компании не отставать от Microsoft с её Xbox 2.

Уже упоминавшаяся ориентация Cell не только на консоли, но и на сервера "на руку" IBM. "Голубой гигант" уже неоднократно заявлял, что "клетки" могут применяться в различных компьютерах: от ПК и рабочих станций до серверов и суперкомпьютеров. Не будем забывать и о словах IBM, согласно которым стандартная стойка двухпроцессорных серверов на базе Cell обеспечит производительность в 16 Терафлоп.

Но сервера - не единственное применение Cell в качестве "серьёзного" чипа. Благодаря высокой производительности, малому энергопотреблению и изначальной ориентированности на распределённые вычисления, новый процессор может найти применение и в суперкомпьютерах. Вспомним "клеточную архитектуру" IBM 2000 года. На её основе был создан суперкомпьютер Blue Gene/L, с 16 сентября 2004 года и до недавнего времени (до появления SGI Columbia supercomputer) занимавший первую позицию в списке Top500. 36 Терафлоп его производительности обеспечивают 32 тысячи основанных на базе улучшенного 32-разрядного ядра PowerPC 440 SoC-микропроцессоров с частотой 700 МГц. Посредством высокоскоростных шин чипы соединены с другими, образуя символический "гиперкуб". Теперь подсчитайте, какая производительность была бы достигнута, замени IBM старые процессоры Blue Gene/L на Cell?

Применение Cell в суперкомпьютерах позволит, по словам Кена Кутараги, поднять их производительность до 1 Петафлопа/с, тем самым, дав зелёный свет для появления настоящего ИИ (искусственного интеллекта).

Следующая область применения Cell - компьютеры Macintosh. Несмотря на конкуренцию между Apple и Sony, на выставке MacWorld 2005 на сцене со Стивом Джобсом (Steve Jobs) присутствовал сам президент японской корпорации Кунитаке Ано (Kunitake Ando). Джобс собирался: "поговорить о сотрудничестве между Apple и Sony для создания в этом году видео высокой чёткости", на что Андо ответил: "стратегически для Sony очень важна возможность работы с Apple, компанией, выпускающей отличные приложения, работающие со всеми продуктами Sony. И новое ПО, которое вы только что представили - просто сделайте это. На Mac-платформе".

Трудности IBM с выпуском мобильных процессоров PowerPC 970FX заставляют Apple, планирующую выпустить PowerBook G5 уже второй год, искать выход из сложившейся ситуации. И, вполне возможно, Cell, являясь, по сути, PowerPC-процессором с DSP-чипами в придачу, призван её разрешить. Присутствие же в PPE блока VMX при наличии восьми самостоятельных векторных процессоров SPE наводит на мысль о том, что STI хотела бы, чтобы Cell работал со "старым" ПО. А большая часть программ в мире, использующих VMX, являются MacOS-программами.

Кроме того, сама Apple разрабатывает технологии Core Image и Core Video (MacOS X Tiger), направленные на использование не AltiVec (VMX), а графического процессора видеокарты, что может говорить о желании компании оставить VMX в покое.

Существует три варианта развития событий. Первый - Apple будет продолжать использовать процессоры PowerPC 970FX/970MP. Второй - Cell будет применён в ноутбуках компании, тогда как PowerPC 970FX/970MP - в остальных продуктах. И, наконец, третий - Apple полностью перейдёт на Cell, используя его во всех своих компьютерах.

Правильный ответ даст нам конференция WWDC 2005 летом или MacWorld 2006 следующей зимой. Кроме Apple представители STI заявляют, что Cell будет поставляться всем производителям, желающим использовать его в своей продукции. Трио гигантов индустрии (STI) и "процессор нового поколения" заставляют задуматься многих. Например, известно, что компания Genesi, производящая материнские платы Pegasos, всерьёз задумывается об использовании Cell в своих будущих продуктах.

Но не только в полноценных компьютерах может использоваться "клетка". Многие говорят о возможности выпуска PCI/PCI-E-карт с установленным на них Cell. Работая параллельно с основным процессором под различными ОС (той же WindowsXP), он будет выполнять роль ускорителя (попросту - "числодробилки"). Правда, есть и те, кто предсказывает возможное игнорирование Microsoft нового процессора. Опасения их не беспочвенны, так как множество высокопроизводительных чипов, созданных небольшими компаниями и предназначенных в качестве "сопроцессора" к основному CPU, канули в свет именно из-за недостаточной программной поддержки. Но надежда, причём весьма большая, есть: благодаря намного большей распространённости Cell в мире написание необходимого ПО не должно заставить себя долго ждать.

Большой объём статьи не позволяет описать все устройства, где может применяться Cell. Но Вы можете сделать это самостоятельно: представьте себе технику начала XXI века, которой необходим сверхбыстрый, экономичный и дешёвый процессор. Cell как раз для неё.

Свет в конце туннеля

На сегодняшний день продажи PlayStation 2 составляют свыше 80 миллионов штук, что, само собой разумеется, означает продажу такого же количества Emotion Engine. Вследствие дальнейшего развития архитектуры Cell, цифра продаж PlayStation 3 может быть ещё выше. Для создания Sony и Toshiba десятков миллионов HDTV-телевизоров, Blu-Ray-рекордеров и прочей цифровой техники потребуется такое же количество Cell. Ориентация новой архитектуры на серверы и суперкомпьютеры подразумевает необходимость в большом количестве Cell для их создания/производства (вспомним про 32 тысячи процессоров в Blue Gene/L).

Если догадки экспертов окажутся верны, при использовании нового чипа Apple количество Cell в мире может достигнуть сотен миллионов штук. При этом "за кадром" осталась возможность "поштучной" продажи Cell на манер Pentium/Athlon, использование процессора в качестве DSP-чипа и т.д. В итоге можно сделать вывод: Cell будет намного более распространённым процессором, чем Emotion Engine. Пусть не в персональных компьютерах и серверах (побудем скептиками), но количество - есть количество.

И если в далёком 2000 году Кен Кутараги, как ребёнок, кричал, что выступит один против непобедимой на протяжении уже второго десятка лет Intel, то сегодня SCEI - уже не та "самонадеянная девчонка", затеявшая "дразниться со взрослыми". Теперь за её плечами не только Toshiba и IBM, но и другие компании. Расклад изменился. Осталось лишь дождаться и посмотреть, что же произойдёт при "вскрытии карт"?

Послесловие, или P.S

Для того чтобы статья не казалась чересчур радужной, позаимствуем для неё пару "чёрных пятен" с Солнца. Некоторые обозреватели опасаются того, что Cell, как и Emotion Engine, будет очень тяжело программировать. Обеспечение одновременной работы, по сути, девяти процессоров сведёт на "нет" все технические достоинства нового чипа. Однако IBM довольно долгое время работает над средствами разработки программ для Cell. На данный момент SDK представляет собой широко распространенный компилятор GCC, обогащённый макросами для копирования информации между SPE и памятью (как локальной самого SPE, так и оперативной). Кроме того, в состав пакета будут входить специальные алгоритмы, распределяющие задачи между SPE, и облегчающие тем самым перенос приложений из других архитектур/операционных систем. Разработка SDK продолжается, и к моменту выхода Cell должна быть полностью завершена.

Слышатся крики по поводу поддержки Cell рынком программного обеспечения и, в первую очередь, операционными системами. Скажем следующее: недавно IBM продала свой бизнес по производству ПК китайской компании Lenovo, сосредоточив все усилия на разработке Linux, и именно IBM занимается переносом этой ОС на Cell. Мягко говоря, довольно распространённая система, особенно среди программистов, да и новые программы к ней появляются, "как грибы после дождя". Перенос их на Cell не составит особых проблем (оптимизация под SPE потребует некоторых усилий, но это уже другой вопрос).

У Apple есть MacOS X, самая приветливая и лёгкая в использовании операционная система, которую, по словам самого Стива Джобса, с недавних пор производители ПК первого эшелона хотят видеть на своих компьютерах. Если Cell будет использован в продукции Apple, MacOS X (а вместе с ней и ПО ведущих компаний-разработчиков) будет перенесена на этот процессор .

В конце концов, даже сама Microsoft перенесла WindowsXP (или её родственницу) на PowerPC, чтобы использовать в своей Xbox 2. Авось "умелые руки" заставят её работать с "клеткой"?

Так что не всё так плохо, как сперва кажется. Перевернём страницу прошлого и, с надеждой на светлое будущее, будем смотреть вперёд, где Cell светит яркой звёздочкой.

Примечание: В статье использованы фотографии и блок-схемы с сайта pc.watch.impress.co.jp