TSMC подтвердила отставание от Intel во внедрении передовых полупроводниковых технологий

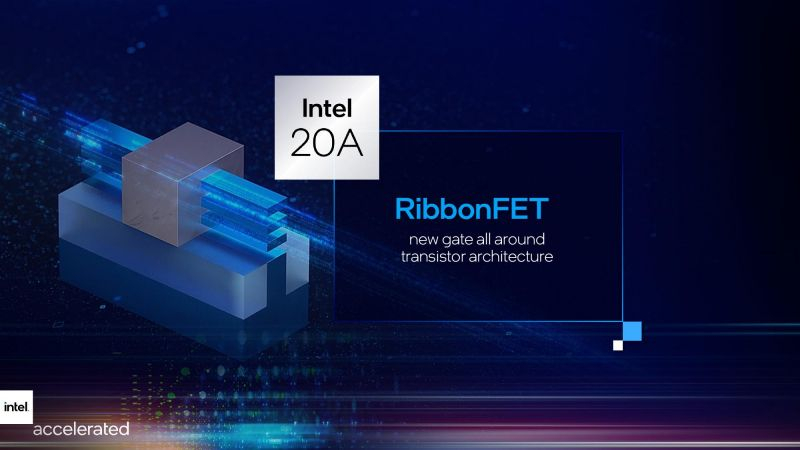

Компания Intel последние полтора года буквально на каждом углу твердит, что намерена вернуть себе технологическое лидерство в сфере литографии к 2025 году. К тому времени она собирается освоить техпроцесс Intel 18A, а годом ранее в рамках технологии 20A она начнёт применять транзисторы со структурой RibbonFET и схему PowerVIA с подводом питания с обратной стороны чипа. Если опираться на новые комментарии представителей TSMC, тайваньский конкурент Intel последнее из новшеств своим клиентам предложит не ранее 2026 года.

Источник изображения: Intel

На минувшей квартальной отчётной конференции генеральный директор TSMC Си-Си Вэй (C.C. Wei) заявил, что техпроцесс N2 осваивается компанией в полном соответствии с графиком, и в массовом производстве он будет внедрён в 2025 году. TSMC в рамках технологии N2 будет использовать новую структуру транзисторов с так называемыми нанолистами (с круговым затвором) — Intel же её разновидность по имени RibbonFET при удачном стечении обстоятельств рассчитывает внедрить уже в 2024 году. Как считает глава TSMC, технология нанолистов предложит клиентам компании в рамках норм N2 лучшее сочетание производительности и энергопотребления на рынке, а также самую высокую плотность размещения транзисторов. Это позволит TSMC укрепить своё технологическое лидерство к моменту появления техпроцесса N2 на рынке, как считают в компании.

Однако следует учесть, что Intel свою структуру RibbonFET собирается внедрить в рамках техпроцесса 20A уже в следующем году — по крайней мере, на уровне прототипов. С этой точки зрения, если учитывать упоминания представителей TSMC о внедрении нанолистов в 2025 году, американский производитель чипов может претендовать на лидерство по срокам внедрения подобного новшества.

Генеральный директор TSMC попутно напомнил, что в рамках семейства техпроцессов N2 компания собирается внедрить и схему питания с обратной стороны чипа. По его словам, это новшество будет больше востребовано в сегменте высокопроизводительных вычислений. Скорость переключения транзисторов оно позволит поднять на 10–12 %, а плотность размещения транзисторов увеличить на 10–15 % по сравнению с базовым вариантом N2. Технически TSMC предложит данную схему питания чипов уже во второй половине 2025 года, но потребителям она станет доступна в массовом производстве лишь в 2026 году. Это значит, что и здесь TSMC тоже отстанет от Intel, причём сразу на полтора или два года, если в планах последней не возникнет непредвиденных задержек.

Глава TSMC добавил, что компания наблюдает высокий интерес клиентов к техпроцессам семейства N2 как со стороны разработчиков высокопроизводительных чипов, так и в сегменте смартфонов. В ходе беседы с аналитиками на отчётном мероприятии представители TSMC были вынуждены признать, что по мере смены техпроцессов компании удаётся повышать быстродействие транзисторов на всё меньшую величину. В рамках техпроцессов N2 достичь заметного прироста производительности по прежним меркам тоже не удастся, но клиенты в последнее время всё чаще заостряют внимание на повышении энергоэффективности, поэтому компания решила уделить этой оптимизации должное внимание при освоении данной литографической технологии. В сегменте центров обработки данных, по словам главы TSMC, это очень ценится.