Настольные процессоры нового поколения Intel Core Ultra 200S поступят в продажу 24 октября. По этому случаю китайский офис компании Asus решил опубликовать видео, в котором рассказал о материнских платах на чипсете Intel Z890, предназначенных для этих чипов. В этом ролике компания также в деталях рассказала об особенностях архитектуры самих процессоров Intel.

Источник изображений: Asus

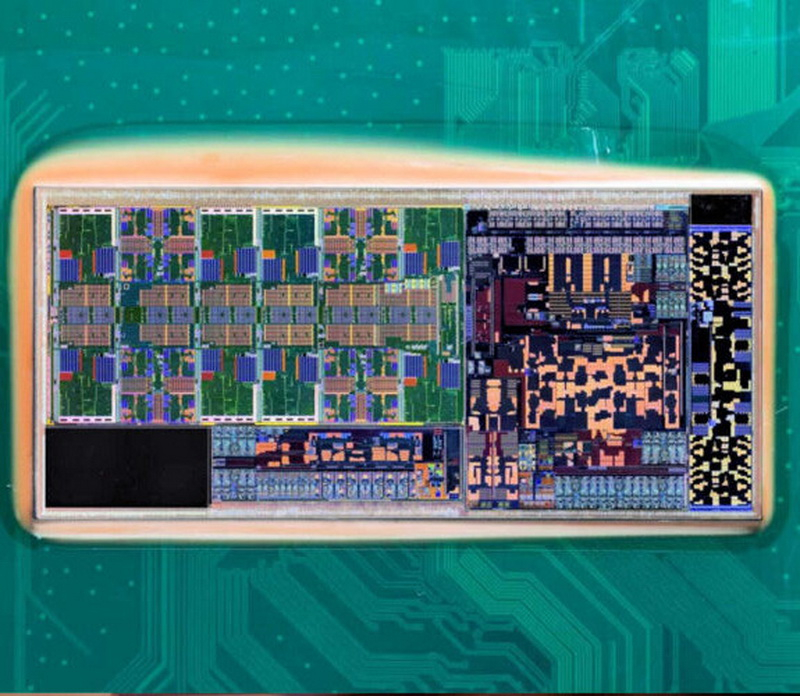

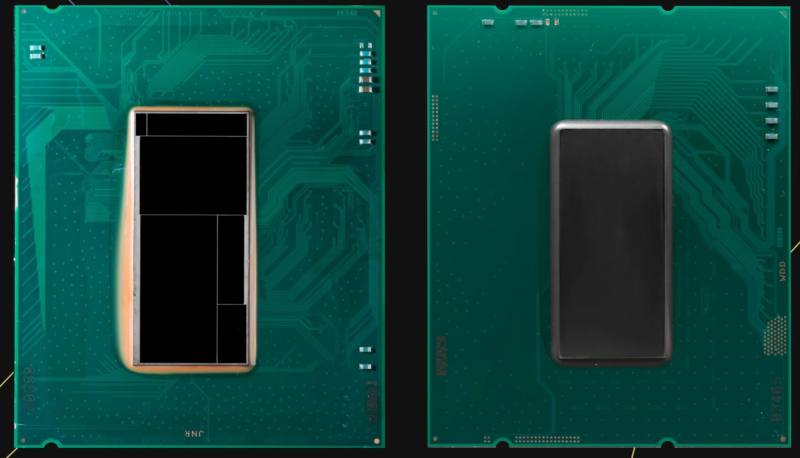

Asus не только сняла теплораспределительную крышку с одного из процессоров серии Core Ultra 200S, но также убрала верхний кремниевый слой с его четырёх чиплетов, чтобы рассказать об их особенностях.

Процессоры Core Ultra 200S состоят из четырёх логических компонентов (плиток или чиплетов), объединённых на подложке Foveros: вычислительного чиплета с ядрами CPU, кристалла SoC, блока встроенной графики (iGPU), а также кристалла интерфейсов ввода-вывода (I/O Die). У Core Ultra 200S также имеются два чиплета-пустышки, которые на предоставленных Asus изображениях выглядят как пустоты (чёрные области).

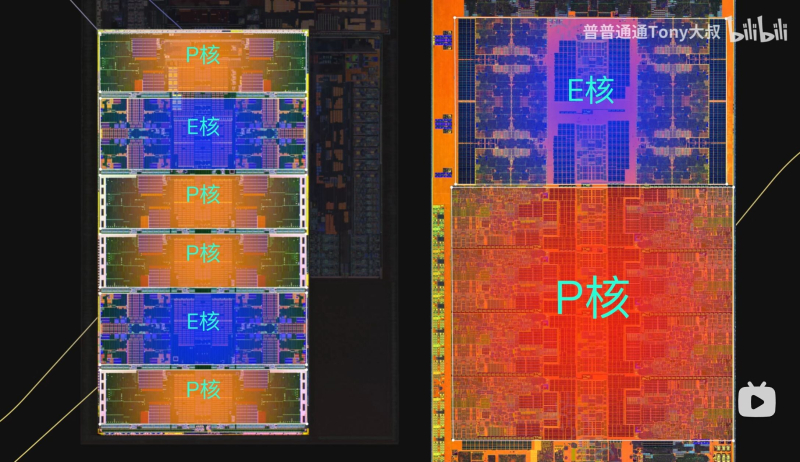

Вычислительный чиплет с ядрами производится на базе самого передового технологического процесса среди четырёх кристаллов в составе Core Ultra 200S — TSMC N3B класса 3 нм. В отличие от предыдущих поколений процессоров Raptor Lake-S и Alder Lake-S у новых Arrow Lake-S производительные P-ядра и энергоэффективные E-ядра не сгруппированы друг с другом. Большие и малые ядра процессоров Core Ultra 200S расположены поочерёдно: за рядом P-ядер следует кластер E-ядер, за которым следует два ряда P-ядер, а после них ещё один кластер E-ядер перед последним рядом P-ядер. В конечном итоге получается конфигурация из восьми P-ядер и 16 E-ядер. Такая схема расположения ядер снижает концентрацию тепла при загрузке P-ядер (например, во время игр) и гарантирует, что каждый кластер E-ядер находится всего в одном шаге от кольцевой шины и от P-ядра, что должно улучшить задержки миграции потоков. Сама кольцевая шина, а также 36 Мбайт кеш-памяти L3, совместно используемой P- и E-ядрами, находятся в центральной области чиплета.

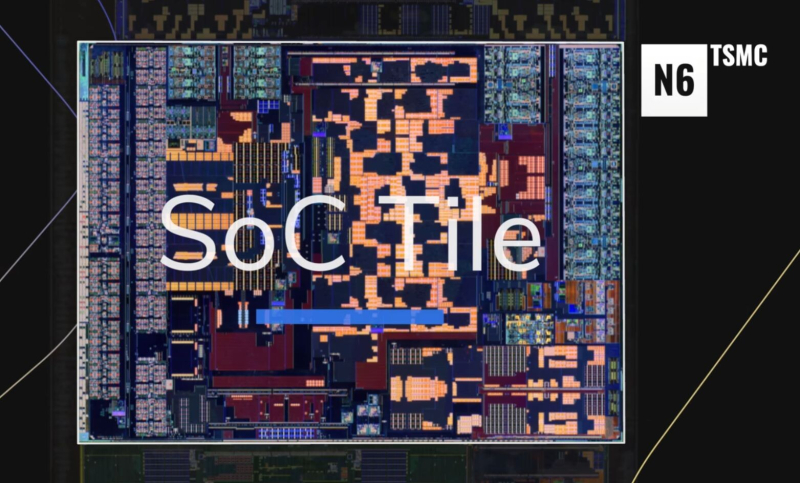

Чиплет SoC процессоров Core Ultra 200S производится по 6-нм техпроцессу TSMC N6 с применением литографии в глубоком ультрафиолете. По обоим концам кристалла расположены схемы PHY, отвечающие за работу различных интерфейсов ввода-вывода. На одной стороне чиплета расположена схема PHY для DDR5, на другой — для PCI Express. Чиплет SoC обеспечивает поддержку 16 линий PCIe 5.0 для разъёмов PCIe x16 на материнской плате. В составе SoC присутствует блок NPU (ИИ-ускоритель), который, судя по всему, позаимствован у SoC процессоров Meteor Lake. Его пиковая ИИ-производительность составляет 13 TOPS (триллионов операций в секунду). Также в составе SoC присутствует сопроцессоры безопасности платформы, а также некоторые элементы iGPU, включая контроллер дисплея (Display Engine), ускорители мультимедиа и т.д.

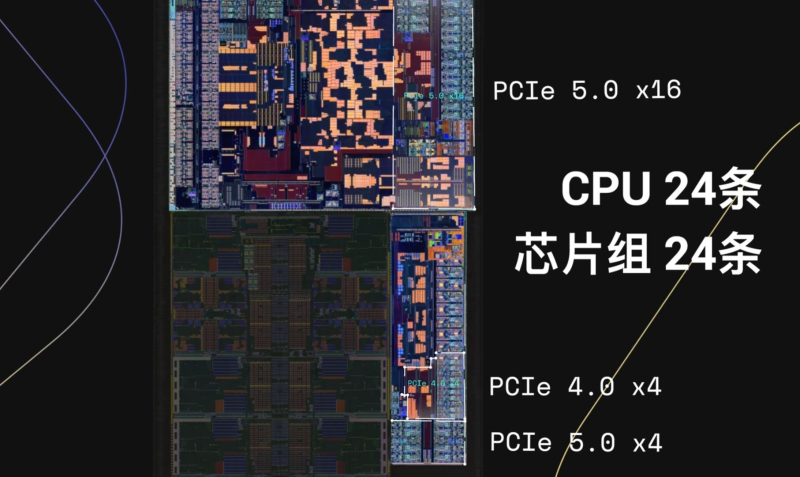

Помимо шины чипсета DMI 4.0 x8 чиплет I/O (тоже 6-нм техпроцесс TSMC N6) обеспечивает работу четырёх линий PCIe 5.0 и четырёх PCIe 4.0 для NVMe-накопителей. Линии PCIe 4.0 из I/O-чиплета можно переконфигурировать для поддержки интерфейсов Thunderbolt 4 или USB4.

Чиплет встроенной графики (iGPU) процессоров Core Ultra 200S производится с применением 5-нм техпроцесса TSMC N5. С использованием этого же техпроцесса (одной из его версий) выпускаются графические процессоры актуальных видеокарт Nvidia с архитектурой Ada Lovelace и AMD с RDNA 3. В составе этого чиплета присутствуют четыре графических ядра Xe, а также различные элементы для рендеринга изображения.

Источник:

MWC 2018

MWC 2018 2018

2018 Computex

Computex

IFA 2018

IFA 2018

Подписаться

Подписаться