|

Опрос

|

реклама

Быстрый переход

«Последний рубеж транзисторной архитектуры»: TSMC и Intel рассказали о нанолистовых транзисторах

13.12.2024 [13:02],

Геннадий Детинич

На днях на конференции IEDM 2024 в Сан-Франциско компания TSMC впервые официально рассказала о преимуществах перехода на 2-нм транзисторы с круговым затвором Gate-All-Around и нанолистовыми каналами. К выпуску чипов по технологии N2 тайваньский чипмейкер приступит в наступающем году. По сути, нанолисты — это финальная архитектура транзисторов в привычном понимании и она останется актуальной надолго.

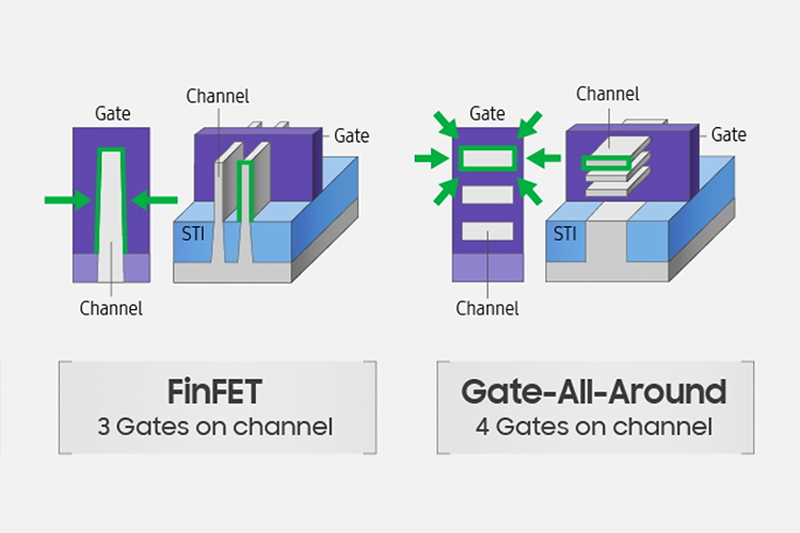

Не видите внизу 2-нм транзисторы? А они есть! Источник изображения: TSMC В 2025 году производить чипы на основе 2-нм техпроцесса с наностраничными каналами и круговым затвором начнут также Samsung и Intel. Подобные структуры первой начала выпускать компания Samsung в рамках 3-нм техпроцесса в 2022 году. Для TSMC это станет первым опытом и плодом «более чем четырёхлетнего труда», как признался глава отдела разработчиков компании. Современные транзисторы FinFET представляют собой набор вертикально расположенных транзисторных каналов — рёбер или плавников. Характеристики такого транзистора зависят от количества рёбер у каждого — одного, двух или трёх. Чем больше каналов, тем больше площадь, занимаемая транзистором. Это особенно остро сказывается в случае массивов памяти SRAM. Каждая ячейка такой памяти состоит из шести транзисторов и поэтому плохо поддаётся масштабированию. Между тем, без SRAM не обходятся ни простенькие контроллеры, ни мощные процессоры и ускорители. Перевод транзисторных каналов в горизонтальную плоскость в виде тонких наностраниц сразу улучшает плотность, так как каналы располагаются друг над другом, и неважно, сколько их. От этого занимаемое транзистором место не увеличивается. В частности, переход TSMC от выпуска 3-нм FinFET транзисторов к 2-нм наностраничным увеличивает плотность размещения транзисторов на 15 %, независимо от того, используются ли производительные схемы или энергоэффективные. Выигрыш произойдёт в обоих случаях. Между производительностью и энергоэффективностью придётся выбирать. Если делать ставку на скорость вычислений, прирост от перехода на 2-нм наностраничные транзисторы составит 15 %, а если выбрать низкое потребление, то выигрыш достигнет впечатляющих 30 %. Но это не вся польза от наностраничных каналов. Для FinFET транзисторов нельзя создать транзисторы с 1,5 рёбрами — это как полтора землекопа из известной сказки. Зато в случае наностраничных каналов можно менять их ширину, не говоря о количестве, и проектировать схемы с разнообразными и точно требуемыми параметрами. В компании TSMC технологию изменения ширины наностраниц назвали Nanoflex. Это позволит выпускать на одном кристалле логику с узкими наностраницами, что ограничит их потребление, и вычислительное ядро с транзисторами с широкими наностраницами для пропускания больших токов, что обеспечит производительность, несмотря ни на что. Но особенно заметно от перехода на наностраничные транзисторные каналы выиграет SRAM. При переходе с 4-нм на 3-нм техпроцесс плотность ячеек памяти SRAM выросла всего на 6 %. В случае технологии Nanoflex при переходе от 3-нм на 2-нм техпроцесс плотность ячеек SRAM вырастет на 11 %. Это даст повсеместный выигрыш, утверждают в TSMC.

Источник изображения: Intel Интересно добавить, что на этой же конференции прозвучал доклад компании Intel, которая очертила границы будущего для классических транзисторов и, конкретно, в наностраничном исполнении. «Архитектура наностраниц на самом деле является последним рубежом транзисторной архитектуры, — сказал Ашиш Агравал (Ashish Agrawal), специалист по кремниевым технологиям в исследовательской группе Intel по компонентам схем. — Даже будущие комплементарные FET (CFET) устройства, которые, возможно, появятся в середине 2030-х годов, будут построены из нанолистов. Поэтому важно, чтобы исследователи понимали свои ограничения». Чтобы изучить границы возможного, в Intel создали экспериментальную транзисторную структуру с каналом длиной 6 нм. Чем короче канал, тем выше вероятность утечек через него и тем менее управляемым становится транзистор. Эксперимент показал, что транзисторы с каналами длиной 6 нм и шириной наностраницы 2 нм полностью работоспособны. Это позволит наностраничной транзисторной архитектуре существовать ещё долго, отодвинув переход на двумерные материалы и транзисторы на принципиально иной архитектуре далеко в будущее. Возвращаясь к 2-нм техпроцессу TSMC (а также Samsung и Intel), напомним, что цифра в его названии ничего не говорит о физических размерах транзисторов. В рамках 2-нм техпроцесса транзисторы и транзисторные каналы измеряются десятками нанометров. Поэтому до выставленных Intel границ в эксперименте индустрия будет идти не одну пятилетку. IBM и Rapidus придумали, как сделать 2-нм чипы производительными или энергоэффективными

10.12.2024 [15:07],

Геннадий Детинич

Компании IBM и Rapidus для конференции IEDM 2024 подготовили доклад, в котором сообщили о продвижении к массовому производству 2-нм чипов. Партнёры разработали метод выпуска как высокопроизводительных, так и малопотребляющих модификаций 2-нм чипов. Оба техпроцесса полностью управляемы и до конца десятилетия будут реализованы на практике в Японии на заводе компании Rapidus.

Источник изображения: IBM Компания IBM начала разрабатывать транзисторы с круговым затвором (GAA, Gate-All-Around) на основе стопки транзисторных каналов из наностраниц более 10 лет назад совместно с компанией Samsung. Затем их пути разошлись. Компания Samsung начала самостоятельно развивать идею GAA-транзисторов, а компания IBM два года назад взяла в партнёры японскую компанию Rapidus, которую создали в качестве японского ответа TSMC. Партнёры стремятся к тому, что с 2027 года Rapidus станет центром мирового контрактного производства полупроводников. Такое вполне возможно, если с TSMC вдруг случится что-то непоправимое, а в Тихоокеанском регионе в ближайшие пять лет может произойти много изменений. При переходе на выпуск 2-нм транзисторов все производители, включая IBM и Rapidus, отказались от «плавниковых» транзисторов FinFET. Каналы транзисторов вернули из вертикального положения в горизонтальное и представили их в виде нескольких уровней нанопроводов или наностраниц, расположенных друг над другом в рамках одного транзистора. Каналы получились в виде наноструктур, полностью окружённых затворами. Это позволило сохранить рабочие токи, хотя сами транзисторы стали ещё мельче. Перед компаниями стояла задача массового производства маленьких транзисторов, так, чтобы отдельные компоненты не загрязнялись материалами, предназначенными для других. Компании IBM и Rapidus во многом справились с этой проблемой, а также показали возможность выпускать GAA-транзисторы с несколькими пороговыми напряжениями в каналах: с высокими для малопотребляющей электроники и с низкими для высокопроизводительной. На конференции IEDM 2024 IBM и Rapidus представили технологию выборочного уменьшения слоя (selective layer reductions) — пространства между полупроводниковыми каналами n-типа и p-типа. В зависимости от толщины этого пространства пороговое напряжение будет изменяться от большего к меньшему. Толщина задаётся на этапе производства транзисторов и определяет, каким будет чип — производительным или энергоэффективным. Партнёры представили два варианта техпроцесса: SLR1 и SLR2. Техпроцесс SLR1 обеспечивает высокое значение порогового напряжения, а SLR2 — низкое. Также компании IBM и Rapidus смогли значительно снизить загрязнение изолирующей подложки под транзисторами ионами в процессе плазменной обработки чипов в процессе производства — травления. Кадзуюки Томида (Kazuyuki Tomida), генеральный менеджер Rapidus US, также отметил: «Технология Multi-Vt [мультипороговых напряжений] является важнейшим компонентом нашей архитектуры наностраниц. Совместная публикация этого исследовательского документа с IBM Research на конференции IEDM представляет собой важную веху для Rapidus. Это достижение укрепляет нашу уверенность в реализации нашей цели — производстве на Хоккайдо на нашем передовом полупроводниковом заводе IIM». Японская Rapidus запустит пилотное производство 2-нм чипов уже в 2025 году

20.06.2024 [20:07],

Сергей Сурабекянц

Японский стартап Rapidus планирует открыть пилотное производство 2-нм чипов в апреле 2025 года, сообщил генеральный директор Ацуёси Койке (Atsuyoshi Koike). В освоении передового техпроцесса компании помогает IBM и глобальная научно-исследовательская организация Imec. Инновационная технология обработки пластин должна обеспечить Rapidus конкурентное преимущество перед TSMC и Samsung за счёт сокращения продолжительности производственного цикла. Источник изображения: Samsung «Если стоимость одинаковая, если я могу обеспечить [время цикла] в два-три раза меньше, чем на обычном заводе, что предпочтёт заказчик? — рассуждает Койке. — Мы недостаточно быстры, чтобы перейти на 2 нм [раньше TSMC], но мы можем наверстать упущенное, потому что у нас есть высокоскоростная обратная связь, позволяющая быстро наращивать темпы». По словам аналитика Albright Stonebridge Group Пола Триоло (Paul Triolo), предсказать успех амбициозного проекта сложно: «У фирмы компетентное руководство, мощная поддержка правительства Японии и уважаемые технологические партнёры, такие как Imec и IBM. Но клиенты должны быть уверены, что передовые технологические процессы, впервые разработанные командой Rapidus-IBM-Imec, способны обеспечить привлекательную производительность и стоимость на одном уровне с мировыми лидерами TSMC и Samsung». Rapidus, в число инвесторов которой входят Sony, Denso, Toyota, SoftBank и Kioxia, потребуется больше внешних инвестиций, чтобы начать коммерческое производство. По оценкам Койке, его компании понадобится в общей сложности 5 триллионов йен (около 31,8 миллиарда долларов). При этом правительство Японии готово предоставить Rapidus субсидии на основе годовых результатов. Компания планирует добавить в список своих партнёров больше разработчиков чипов ИИ, таких как Tenstorrent и Esperanto. Койке заявил, что несколько компаний Кремниевой долины заинтересованы в том, чтобы стать их клиентами, но названия компаний он сообщить отказался. Rapidus планирует производить чипы ИИ для маломощных периферийных вычислений, а также мощные чипы для высокопроизводительных вычислений в центрах обработки данных. Rapidus объединяет процессы производства и упаковки чипов, чем традиционно занимаются отдельные компании. По словам Койке, инженеры этих производств «разделены большой стеной». «Никаких обсуждений. Они говорят на разных языках. Я убрал эту стену в своей компании, чтобы они могли говорить друг с другом», — добавил он. Объединение производства и упаковки теоретически может сократить время цикла. В настоящее время Rapidus разрабатывает методы тестирования признанных годных кристаллов (known good die, KGD) и впервые в полупроводниковой промышленности собирается перейти от проектирования процессов (process design kit, PDK) к проектированию сборки (assembly design kit, ADK). Для строительства завода в городе Титосэ на севере японского острова Хоккайдо Rapidus заключила контракт с Kajima, одной из старейших и крупнейших строительных компаний Японии. По данным Rapidus, сейчас на возведении фабрики работает 2000–3000 сотрудников Kajima, а октябрю на этом проекте будет задействовано около 5000 человек.

Источник изображения: Rapidus Сама компания Rapidus уже наняла более 400 инженеров и планирует ежегодно увеличивать штат ещё на 300 человек. В этом году компания отправит около 200 из них в США для освоения 2-нм технологии, разработанной IBM. Аналитики полагают, что компания столкнётся со значительными проблемами в привлечении персонала, учитывая спрос на квалифицированную рабочую силу в Японии и расширение производственных мощностей конкурентов, таких как TSMC, Western Digital, Micron и Kioxia. Samsung будет выпускать для AMD передовые 3-нм чипы с GAA-транзисторами

01.06.2024 [09:02],

Анжелла Марина

Компания Samsung объявила о расширении стратегического партнерства с американской компанией Advanced Micro Devices (AMD) в области разработки передовой 3-нанометровой технологии производства чипов. Используя более тесные связи с AMD, Samsung стремится обогнать своего главного конкурента, контрактного производителя полупроводников TSMC.

Источник изображения: Samsung Это партнерство позволит компаниям объединить усилия в разработке инновационных решений для производства чипов следующего поколения, которые будут использоваться в высокопроизводительных вычислительных системах, центрах обработки данных, смартфонах и других электронных устройствах. Как сообщает корейское новостное издание KED Globall, в рамках соглашения Samsung, крупнейший в мире производитель микросхем памяти, получит доступ к передовым разработкам AMD в области архитектуры чипов, а AMD, который в свою очередь разрабатывает микропроцессоры и графические процессоры, сможет воспользоваться мощностями Samsung по производству чипов с использованием новейшей 3-нм технологии транзисторов Gate-All-Around (GAA). Данная технология позволяет создавать чипы с рекордной плотностью транзисторов и улучшенными характеристиками производительности. По сравнению с предыдущим поколением 5-нм чипов, 3-нм чипы GAA обеспечивают прирост производительности на 30 %, снижение энергопотребления на 50 % и уменьшение площади чипа на 45 %. В настоящее время Samsung является единственным производителем в мире, который уже запустил 3-нм техпроцесс GAA в коммерческое производство, опередив основного конкурента тайваньскую компанию TSMC. Расширение сотрудничества с AMD позволит Samsung нарастить свою долю на рынке контрактного производства чипов и сократить отставание от TSMC. Известно, что в настоящее время Samsung контролирует около 17 % этого рынка, а TSMC — более 50 %. В дальнейшем Samsung планирует начать массовый выпуск 2-нм чипов на базе технологии GAA в 2025 году, что позволит ей упрочить лидерство в области полупроводниковых технологий. TSMC рассказала, как будет улучшать 2-нм техпроцесс N2 — оптимизация питания в N2P и повышение скорости в N2X

27.04.2023 [10:43],

Геннадий Детинич

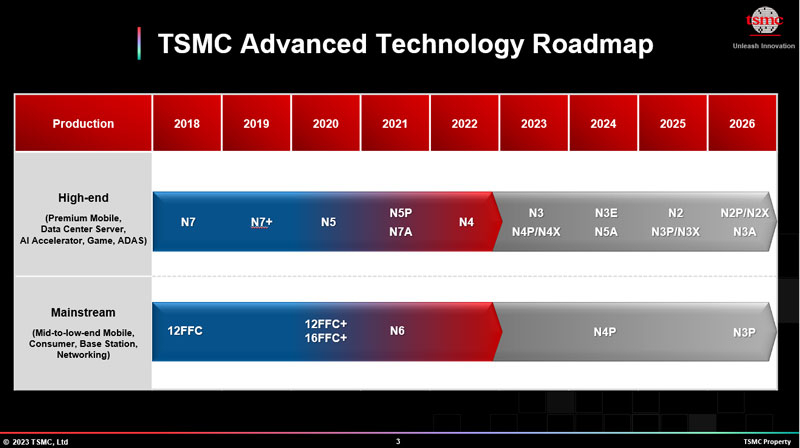

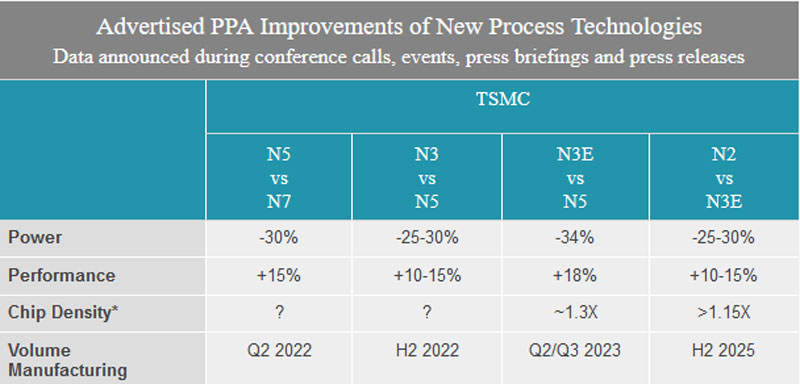

Компания TSMC рассекретила планы совершенствования 2-нм техпроцесса N2, массовое производство по которому должно стартовать в 2025 году. Спустя год после этого будет внедрён оптимизированный по шине питания техпроцесс N2P, а ещё через некоторое время компания запустит техпроцесс N2X для решений с высшей производительностью. Развитие 2-нм техпроцесса TSMC будет стремительным, что может объясняться опасениями TSMC отстать от Intel и Samsung.

Пример транзисторов с вертикальными рёбрами и круговым затвором (справа). Источник изображения: Samsung Официально техпроцесс с нормами 2 нм тайваньский чипмейкер представил летом прошлого года. Производство полупроводников с этими технологическими нормами начнётся в 2025 году. Главной особенностью техпроцесса N2 станет переход с FinFET на транзисторы с круговым затвором (GAAFET). Это снизит токи утечки, позволит гибко регулировать производительность и оптимизирует потребление. Другой важной особенностью техпроцесса N2 должен был стать перенос линий питания чипа на другую сторону кристалла, что будет означать развязку шины данных и управления с питанием.

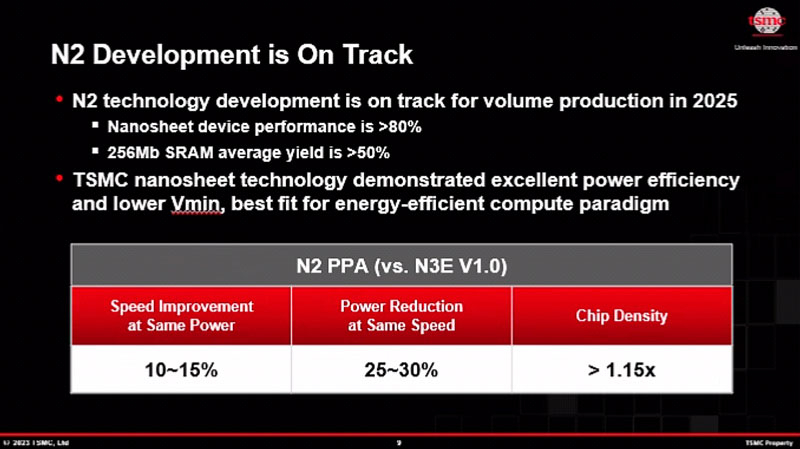

Источник изображений: TSMC Как теперь становится понятно, перенос линий питания ожидается в процессе внедрения техпроцесса N2P, что произойдёт в 2026 году. Из предыдущих заявлений компании первой реализации идеи можно было ожидать в 2025 году. Разнесение интерфейсов питания и данных по разные стороны кристалла решает множество проблем. Так, линии подвода питания к транзисторам станут короче, что снизит их сопротивление. Разнесение разводки уменьшит площадь кристаллов, львиную долю которой съедали линии передачи и межслойные контакты. Наконец, хотя это не всё, снизятся взаимные помехи, что скажется на стабильности сигнальных характеристик чипов.  Снижение площади кристалла, занятой контактами и разводкой, приведёт к значительному увеличению плотности транзисторов. Ранее TSMC заявляла, что переход от техпроцесса с нормами 3 нм к нормам 2 нм увеличит плотность транзисторов на 10 %. К настоящему моменту прогноз был улучшен до 15 % и, в случае внедрения техпроцесса N2P, плотность может вырасти на двухзначную величину, которую компания пока не конкретизирует. Закон Мура вздохнёт ещё раз перед своей смертью.  О техпроцессе N2X, который будет внедряться в 2026 году или позже, компания ничего не сообщила. Можно предположить, что это будет не слишком распространённое предложение, тогда как техпроцесс N2P обещает стать рабочей лошадкой компании на этапе 2-нм производства чипов. Также компания сообщила о прогрессе в подготовке базового 2-нм техпроцесса. Производительность транзисторов GAAFET в составе опытного кремния доходит до 80 % от целевых значений. И это за два года до начала внедрения, что очень и очень хорошо. При этом уровень брака при производстве 2-нм ячеек SRAM объёмом 256 Мбит снизился до 50 % и менее.

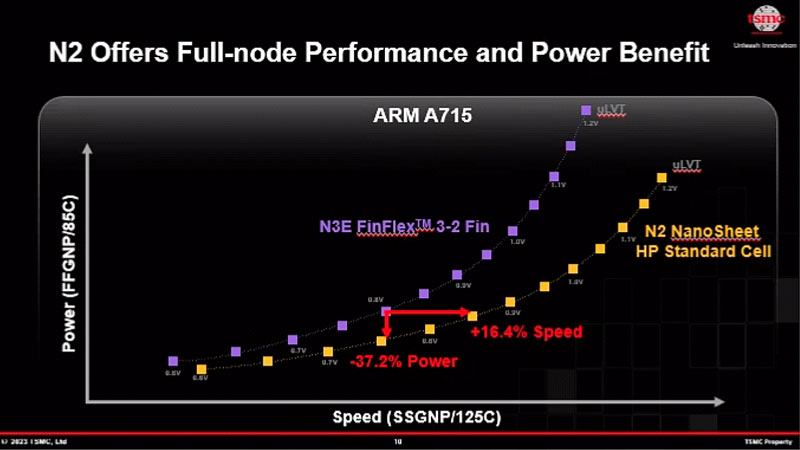

Источник изображения: Anandtech В целом техпроцесс с нормами 2 нм позволит TSMC повысить производительность транзисторов на 10–15 % при той же мощности и сложности, или снизить энергопотребление на 25–30 % при тех же тактовых частотах и количестве транзисторов. На бумаге TSMC отстаёт от компании Intel на год или два и успехи одной из компаний не дают покоя другой. Если каждая из них сдержит обещания, то чипы TSMC с транзисторами GAAFET появятся на два года позже аналогичных чипов Intel (20A), что также касается планов переноса линий питания на обратную сторону кристалла. |