|

Опрос

|

реклама

Быстрый переход

Индия станет производителем полупроводников в этом году — её первые чипы будут 28-нм

24.01.2025 [19:37],

Сергей Сурабекянц

Индийский рынок полупроводников готов к быстрому росту — по прогнозам, его ёмкость достигнет $63 млрд к 2026 году. Индия готовится совершить резкий скачок на мировой технологической арене, а первые чипы индийского производства дебютируют уже в этом году. Хотя они будут выпускаться по далеко не самому современному 28-нм техпроцессу, это будет значительный шаг вперёд, ведь такие чипы широко используются в автомобилестроении, бытовой электронике и интернете вещей.

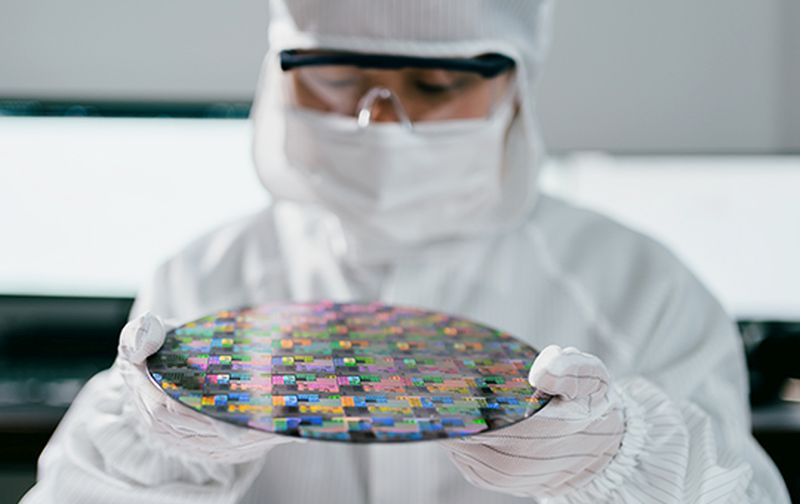

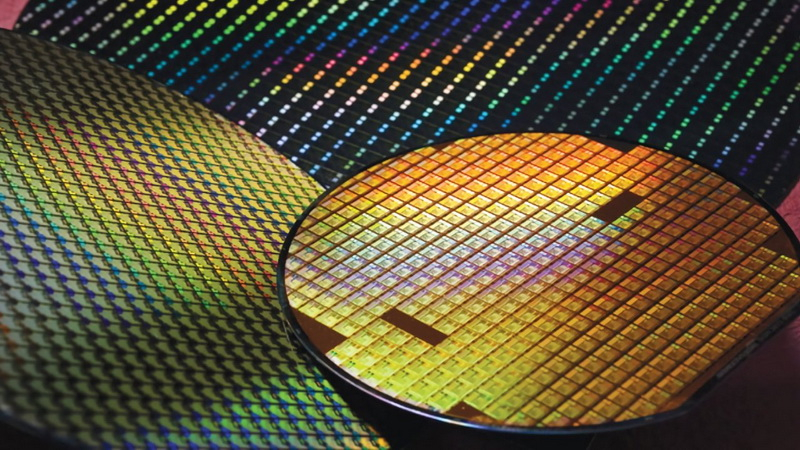

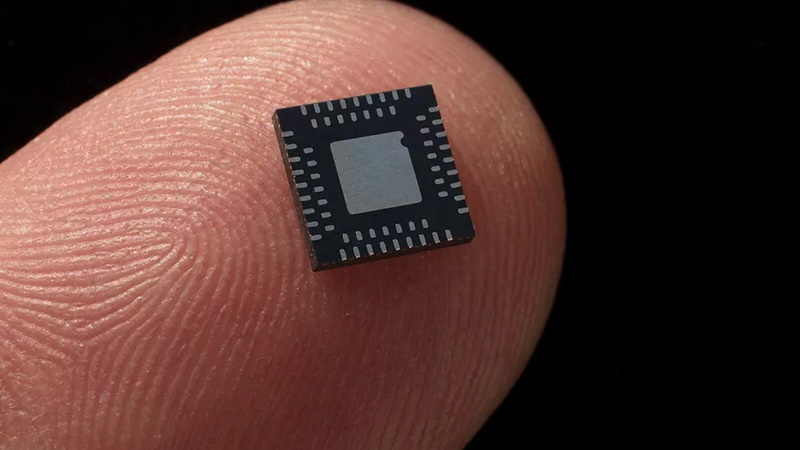

Источник изображения: Micron Первые чипы с маркировкой «Сделано в Индии» изначально планировалось выпустить в декабре 2024 года, но затем срок начала производства был передвинут на август–сентябрь 2025 года. На полную мощность завод по производству полупроводников выйдет в 2026 году при поддержке тайваньской компании Powerchip и индийской промышленной группы Tata. Первые индийские чипы будет выпускаться по 28-нанометровому техпроцессу. Конечно, этот техпроцесс крайне далёк от передовых 2-нм техпроцессов ведущих мировых производителей чипов. Тем не менее, 28-нм чипы широко используются и весьма востребованы в различных отраслях, включая автомобилестроение, бытовую и промышленную электронику и не только. «Наш первый чип будет выпущен в этом году, и теперь мы смотрим на следующий этап, когда мы сможем получить производителей оборудования, производителей материалов и проектировщиков в Индии. Что касается материалов, то от чистоты в частях на миллион нам нужно перейти к уровням чистоты в частях на миллиард. Это требует огромных преобразующих изменений в процессе, и отрасль работает над достижением этого», — заявил на Всемирном экономическом форуме в Давосе министр железных дорог, связи, электроники и информационных технологий Ашвини Вайшнау (Ashwini Vaishnaw). Индия активно работает над развитием своей полупроводниковой промышленности, что обусловлено растущим мировым спросом на чипы и стремлением правительства позиционировать страну как надёжную альтернативу китайским и тайваньским производителям. В частности, в составе Digital India Corporation запущено независимое бизнес-подразделение India Semiconductor Mission. Обладая административной и финансовой автономией, компания будет реализовывать долгосрочные стратегии производства полупроводников и дисплеев, а также содействовать созданию экосистемы проектирования чипов. Индия планирует привлечь значительные иностранные инвестиции. NXP Semiconductors собирается инвестировать в НИОКР полупроводников более $1 млрд. Analog Devices совместно с Tata Group изучает возможности производства чипов. Micron Technology строит в Индии сборочный и испытательный завод стоимостью $2,75 млрд. «Последний рубеж транзисторной архитектуры»: TSMC и Intel рассказали о нанолистовых транзисторах

13.12.2024 [13:02],

Геннадий Детинич

На днях на конференции IEDM 2024 в Сан-Франциско компания TSMC впервые официально рассказала о преимуществах перехода на 2-нм транзисторы с круговым затвором Gate-All-Around и нанолистовыми каналами. К выпуску чипов по технологии N2 тайваньский чипмейкер приступит в наступающем году. По сути, нанолисты — это финальная архитектура транзисторов в привычном понимании и она останется актуальной надолго.

Не видите внизу 2-нм транзисторы? А они есть! Источник изображения: TSMC В 2025 году производить чипы на основе 2-нм техпроцесса с наностраничными каналами и круговым затвором начнут также Samsung и Intel. Подобные структуры первой начала выпускать компания Samsung в рамках 3-нм техпроцесса в 2022 году. Для TSMC это станет первым опытом и плодом «более чем четырёхлетнего труда», как признался глава отдела разработчиков компании. Современные транзисторы FinFET представляют собой набор вертикально расположенных транзисторных каналов — рёбер или плавников. Характеристики такого транзистора зависят от количества рёбер у каждого — одного, двух или трёх. Чем больше каналов, тем больше площадь, занимаемая транзистором. Это особенно остро сказывается в случае массивов памяти SRAM. Каждая ячейка такой памяти состоит из шести транзисторов и поэтому плохо поддаётся масштабированию. Между тем, без SRAM не обходятся ни простенькие контроллеры, ни мощные процессоры и ускорители. Перевод транзисторных каналов в горизонтальную плоскость в виде тонких наностраниц сразу улучшает плотность, так как каналы располагаются друг над другом, и неважно, сколько их. От этого занимаемое транзистором место не увеличивается. В частности, переход TSMC от выпуска 3-нм FinFET транзисторов к 2-нм наностраничным увеличивает плотность размещения транзисторов на 15 %, независимо от того, используются ли производительные схемы или энергоэффективные. Выигрыш произойдёт в обоих случаях. Между производительностью и энергоэффективностью придётся выбирать. Если делать ставку на скорость вычислений, прирост от перехода на 2-нм наностраничные транзисторы составит 15 %, а если выбрать низкое потребление, то выигрыш достигнет впечатляющих 30 %. Но это не вся польза от наностраничных каналов. Для FinFET транзисторов нельзя создать транзисторы с 1,5 рёбрами — это как полтора землекопа из известной сказки. Зато в случае наностраничных каналов можно менять их ширину, не говоря о количестве, и проектировать схемы с разнообразными и точно требуемыми параметрами. В компании TSMC технологию изменения ширины наностраниц назвали Nanoflex. Это позволит выпускать на одном кристалле логику с узкими наностраницами, что ограничит их потребление, и вычислительное ядро с транзисторами с широкими наностраницами для пропускания больших токов, что обеспечит производительность, несмотря ни на что. Но особенно заметно от перехода на наностраничные транзисторные каналы выиграет SRAM. При переходе с 4-нм на 3-нм техпроцесс плотность ячеек памяти SRAM выросла всего на 6 %. В случае технологии Nanoflex при переходе от 3-нм на 2-нм техпроцесс плотность ячеек SRAM вырастет на 11 %. Это даст повсеместный выигрыш, утверждают в TSMC.

Источник изображения: Intel Интересно добавить, что на этой же конференции прозвучал доклад компании Intel, которая очертила границы будущего для классических транзисторов и, конкретно, в наностраничном исполнении. «Архитектура наностраниц на самом деле является последним рубежом транзисторной архитектуры, — сказал Ашиш Агравал (Ashish Agrawal), специалист по кремниевым технологиям в исследовательской группе Intel по компонентам схем. — Даже будущие комплементарные FET (CFET) устройства, которые, возможно, появятся в середине 2030-х годов, будут построены из нанолистов. Поэтому важно, чтобы исследователи понимали свои ограничения». Чтобы изучить границы возможного, в Intel создали экспериментальную транзисторную структуру с каналом длиной 6 нм. Чем короче канал, тем выше вероятность утечек через него и тем менее управляемым становится транзистор. Эксперимент показал, что транзисторы с каналами длиной 6 нм и шириной наностраницы 2 нм полностью работоспособны. Это позволит наностраничной транзисторной архитектуре существовать ещё долго, отодвинув переход на двумерные материалы и транзисторы на принципиально иной архитектуре далеко в будущее. Возвращаясь к 2-нм техпроцессу TSMC (а также Samsung и Intel), напомним, что цифра в его названии ничего не говорит о физических размерах транзисторов. В рамках 2-нм техпроцесса транзисторы и транзисторные каналы измеряются десятками нанометров. Поэтому до выставленных Intel границ в эксперименте индустрия будет идти не одну пятилетку. IBM и Rapidus придумали, как сделать 2-нм чипы производительными или энергоэффективными

10.12.2024 [15:07],

Геннадий Детинич

Компании IBM и Rapidus для конференции IEDM 2024 подготовили доклад, в котором сообщили о продвижении к массовому производству 2-нм чипов. Партнёры разработали метод выпуска как высокопроизводительных, так и малопотребляющих модификаций 2-нм чипов. Оба техпроцесса полностью управляемы и до конца десятилетия будут реализованы на практике в Японии на заводе компании Rapidus.

Источник изображения: IBM Компания IBM начала разрабатывать транзисторы с круговым затвором (GAA, Gate-All-Around) на основе стопки транзисторных каналов из наностраниц более 10 лет назад совместно с компанией Samsung. Затем их пути разошлись. Компания Samsung начала самостоятельно развивать идею GAA-транзисторов, а компания IBM два года назад взяла в партнёры японскую компанию Rapidus, которую создали в качестве японского ответа TSMC. Партнёры стремятся к тому, что с 2027 года Rapidus станет центром мирового контрактного производства полупроводников. Такое вполне возможно, если с TSMC вдруг случится что-то непоправимое, а в Тихоокеанском регионе в ближайшие пять лет может произойти много изменений. При переходе на выпуск 2-нм транзисторов все производители, включая IBM и Rapidus, отказались от «плавниковых» транзисторов FinFET. Каналы транзисторов вернули из вертикального положения в горизонтальное и представили их в виде нескольких уровней нанопроводов или наностраниц, расположенных друг над другом в рамках одного транзистора. Каналы получились в виде наноструктур, полностью окружённых затворами. Это позволило сохранить рабочие токи, хотя сами транзисторы стали ещё мельче. Перед компаниями стояла задача массового производства маленьких транзисторов, так, чтобы отдельные компоненты не загрязнялись материалами, предназначенными для других. Компании IBM и Rapidus во многом справились с этой проблемой, а также показали возможность выпускать GAA-транзисторы с несколькими пороговыми напряжениями в каналах: с высокими для малопотребляющей электроники и с низкими для высокопроизводительной. На конференции IEDM 2024 IBM и Rapidus представили технологию выборочного уменьшения слоя (selective layer reductions) — пространства между полупроводниковыми каналами n-типа и p-типа. В зависимости от толщины этого пространства пороговое напряжение будет изменяться от большего к меньшему. Толщина задаётся на этапе производства транзисторов и определяет, каким будет чип — производительным или энергоэффективным. Партнёры представили два варианта техпроцесса: SLR1 и SLR2. Техпроцесс SLR1 обеспечивает высокое значение порогового напряжения, а SLR2 — низкое. Также компании IBM и Rapidus смогли значительно снизить загрязнение изолирующей подложки под транзисторами ионами в процессе плазменной обработки чипов в процессе производства — травления. Кадзуюки Томида (Kazuyuki Tomida), генеральный менеджер Rapidus US, также отметил: «Технология Multi-Vt [мультипороговых напряжений] является важнейшим компонентом нашей архитектуры наностраниц. Совместная публикация этого исследовательского документа с IBM Research на конференции IEDM представляет собой важную веху для Rapidus. Это достижение укрепляет нашу уверенность в реализации нашей цели — производстве на Хоккайдо на нашем передовом полупроводниковом заводе IIM». В Зеленограде начнут выпускать чипы для SIM-карт и паспортов — на этом планируется заработать триллионы рублей

22.11.2024 [13:45],

Павел Котов

В следующем году предприятие «НМ-Тех» из Зеленограда начнёт запускать проекты, посвящённые производству чипов для SIM-карт, токенов электронных подписей, загранпаспортов, банковских и транспортных карт. До 2030 года компания рассчитывает на совокупную прибыль от реализации этой продукции выше 3 трлн рублей — опрошенные «Коммерсантом» эксперты считают эту цель достижимой.

Источник изображения: JERO SenneGs / unsplash.com На сайте подмосковного завода «НМ-Тех» появилось описание четырёх новых проектов. Это производство микросхем для UHF-меток, которые используются в транспортных и других картах — научно-исследовательские и опытно-конструкторские работы (НИОКР) по нему стартуют в 2025 году, реализация стартует в 2027 году; ожидаемые продажи — 4,8 млрд руб. Защищённые микросхемы для SIM-карт и M2M-чипов для устройств интернета вещей: НИОКР в 2026 году, реализация в 2028 году, продажи — 7,3 млрд руб. Проект по производству U-чип-микросхем, которые используются в загранпаспортах: НИОКР в 2027 году, реализация в 2029 году, продажи — 3,9 млрд руб. Серийное производство чипов для USB-токенов с поддержкой электронной подписи: НИОКР в 2028 году, реализация в 2030 году, объём реализации — почти 3 трлн руб. ООО «НМ-Тех» было зарегистрировано в мае 2019 года; доступ к сведениям о его владельцах и руководителях в ЕГРЮЛ закрыт. В 2022 году организация заключила соглашение с ГК «Элемент» на отладку производства чипов для паспортов и банковских карт на предприятии «Ангстрем-Т» (принадлежит «НМ-Тех»). По итогам 2023 года компания получила 231 млн руб. дохода при чистом убытке 3,3 млрд руб. В начале августа компания зарегистрировала два патента на топологию микросхем для SIM-карт и UHF-меток; уставный капитал летом был увеличен вдвое до 238 млрд руб. Завод «Ангстрем-Т» выпускал всю эту продукцию до 2022 года, но из-за санкций производство пришлось приостановить. Оно возобновится в связи с требованием локализации выпуска банковских и SIM-карт, пропусков и других компонентов с 2026 года. Ежегодный оборот SIM-карт в России оценивается в 100–150 млн штук — их стоимость с начала 2022 года растёт. Сейчас они закупаются преимущественно в Китае, но небольшие партии заказываются и у российских поставщиков, рассказали опрошенные «Коммерсантом» эксперты. Запуск их отечественного производства будет способствовать росту конкуренции на рынке и снижению зависимости от импорта, хотя нельзя пренебрегать такими аспектами как технические требования и финансовые условия поставок. Финансовые ожидания «НМ-Тех» от реализации проектов реалистичны, потому что в России есть спрос на эту продукцию. До начала украинских событий чипы для этой продукции закупались преимущественно у нидерландской NXP Semiconductors, а сейчас Россия сможет их экспортировать — потенциальными покупателями являются государства, находящиеся «под санкционным давлением» и страны Глобального Юга. Поначалу российская продукция будет дороже китайской, но по мере наращивания производства цены будут выравниваться. Samsung представила свой первый 3-нм процессор — Exynos W1000 для будущих смарт-часов

03.07.2024 [13:44],

Николай Хижняк

Компания Samsung представила Exynos W1000 — первый процессор, выпускающийся с использованием её фирменного 3-нм технологического процесса производства. Предполагается, что чип станет основной для новых смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс который состоится на следующей неделе.

Источник изображений: Samsung Samsung сообщила, что Exynos W1000 выполнен с использованием её 3-нм техпроцесса второго поколения (вероятно, SF3). В составе процессора имеются одно ядро Cortex-A78, четыре Cortex-A55, GPU Mali-G68 MP2, поддерживающий экраны с разрешением до 640 × 640 пикселей, а также 32 Гбайт встроенной памяти. По словам компании, новый чип обеспечивает в 2,7 раза более быстрый запуск приложений по сравнению с Exynos W930, а его многопоточная производительность в 3,7 раза выше, чем у предшественника. Для уменьшения размера чипа, повышения его производительности и энергоэффективности Samsung использовала много новых технологий в Exynos W1000. Например, в нём задействуется технология упаковки FOPLP (Fan-Out Panel Level Packaging) для повышения энергоэффективности и лучшего рассеивания тепла. Для оснащение процессора встроенной оперативной и постоянной памятью использовалась технология упаковки ePOP (Package-on-Package). Кроме того, в новом процессоре применяется технология SiP (System-in-Package), благодаря которой в него интегрирован модуль управления питанием (PMIC). Для Exynos W1000 заявляется поддержка технологии 2.5D Always on Display (AoD), которая обеспечивает более качественное отображение изображения и цветов в режиме постоянно включённого дисплея. Кроме того, чип поддерживает Bluetooth LE для передачи звука и энергоэффективную оперативную память стандарта LPDDR5. Для новинки также заявляется поддержка 4G LTE, Bluetooth, Wi-Fi b/g/n, GPS и NFC. Согласно предыдущим слухам и утечкам, Exynos W1000 станет основной для смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс которых ожидается на следующей неделе. Отмечается, что благодаря новым технологиям в составе Exynos W1000 эти устройства Samsung смогут работать в течение 2–3 дней от одного заряда батареи. Samsung с трудом отлаживает 3-нм техпроцесс — уровень брака превышает 80 %

24.06.2024 [20:46],

Николай Хижняк

Компания Samsung с трудом наращивает объёмы выпуска мобильных процессоров Exynos 2500 на основе 3-нм техпроцесса, сообщают аналитики TrendForce со ссылкой на южнокорейское издание ZDNet. Всё дело в огромном проценте брака — к настоящему моменту производитель вышел на уровень годной продукции чуть ниже 20 %.

Источник изображения: Samsung В первом квартале этого года уровень выхода годных чипов составлял однозначное число процентов, так что Samsung постепенно улучшает техпроцесс. Но даже с учётом улучшения производства объёмы выхода небракованных чипов не дотягивает до перехода к массовому выпуску. Остается неясным, будут ли данные процессоры использоваться в составе смартфонов серии Galaxy S25 в будущем, но недавние слухи говорили о том, что будущие флагманы поголовно получат Snapdragon 8 Gen 4. Для эффективного массового производства необходимо, чтобы уровень брака был ниже 40 %. Как сообщается, подразделение System LSI Samsung собирается продолжить работу над повышением качества производственного процесса годных чипов Exynos 2500 во второй половине этого года. Компания намерена выйти на выход годных чипов в 60 % к октябрю. В том же отчёте южнокорейского издания говорится, что главный конкурент Samsung, тайваньский контрактный производитель чипов TSMC, полностью загружен заказами на производство 3-нм продукции для Apple, NVIDIA, AMD, Qualcomm, Intel и MediaTek. В конце мая TSMC сообщала, что утроила производственные мощности для выпуска 3-нм чипов, но этого по-прежнему недостаточно, чтобы покрыть все заказы, поэтому компания всё ещё прилагает усилия для удовлетворения спроса. Японская Rapidus запустит пилотное производство 2-нм чипов уже в 2025 году

20.06.2024 [20:07],

Сергей Сурабекянц

Японский стартап Rapidus планирует открыть пилотное производство 2-нм чипов в апреле 2025 года, сообщил генеральный директор Ацуёси Койке (Atsuyoshi Koike). В освоении передового техпроцесса компании помогает IBM и глобальная научно-исследовательская организация Imec. Инновационная технология обработки пластин должна обеспечить Rapidus конкурентное преимущество перед TSMC и Samsung за счёт сокращения продолжительности производственного цикла. Источник изображения: Samsung «Если стоимость одинаковая, если я могу обеспечить [время цикла] в два-три раза меньше, чем на обычном заводе, что предпочтёт заказчик? — рассуждает Койке. — Мы недостаточно быстры, чтобы перейти на 2 нм [раньше TSMC], но мы можем наверстать упущенное, потому что у нас есть высокоскоростная обратная связь, позволяющая быстро наращивать темпы». По словам аналитика Albright Stonebridge Group Пола Триоло (Paul Triolo), предсказать успех амбициозного проекта сложно: «У фирмы компетентное руководство, мощная поддержка правительства Японии и уважаемые технологические партнёры, такие как Imec и IBM. Но клиенты должны быть уверены, что передовые технологические процессы, впервые разработанные командой Rapidus-IBM-Imec, способны обеспечить привлекательную производительность и стоимость на одном уровне с мировыми лидерами TSMC и Samsung». Rapidus, в число инвесторов которой входят Sony, Denso, Toyota, SoftBank и Kioxia, потребуется больше внешних инвестиций, чтобы начать коммерческое производство. По оценкам Койке, его компании понадобится в общей сложности 5 триллионов йен (около 31,8 миллиарда долларов). При этом правительство Японии готово предоставить Rapidus субсидии на основе годовых результатов. Компания планирует добавить в список своих партнёров больше разработчиков чипов ИИ, таких как Tenstorrent и Esperanto. Койке заявил, что несколько компаний Кремниевой долины заинтересованы в том, чтобы стать их клиентами, но названия компаний он сообщить отказался. Rapidus планирует производить чипы ИИ для маломощных периферийных вычислений, а также мощные чипы для высокопроизводительных вычислений в центрах обработки данных. Rapidus объединяет процессы производства и упаковки чипов, чем традиционно занимаются отдельные компании. По словам Койке, инженеры этих производств «разделены большой стеной». «Никаких обсуждений. Они говорят на разных языках. Я убрал эту стену в своей компании, чтобы они могли говорить друг с другом», — добавил он. Объединение производства и упаковки теоретически может сократить время цикла. В настоящее время Rapidus разрабатывает методы тестирования признанных годных кристаллов (known good die, KGD) и впервые в полупроводниковой промышленности собирается перейти от проектирования процессов (process design kit, PDK) к проектированию сборки (assembly design kit, ADK). Для строительства завода в городе Титосэ на севере японского острова Хоккайдо Rapidus заключила контракт с Kajima, одной из старейших и крупнейших строительных компаний Японии. По данным Rapidus, сейчас на возведении фабрики работает 2000–3000 сотрудников Kajima, а октябрю на этом проекте будет задействовано около 5000 человек.

Источник изображения: Rapidus Сама компания Rapidus уже наняла более 400 инженеров и планирует ежегодно увеличивать штат ещё на 300 человек. В этом году компания отправит около 200 из них в США для освоения 2-нм технологии, разработанной IBM. Аналитики полагают, что компания столкнётся со значительными проблемами в привлечении персонала, учитывая спрос на квалифицированную рабочую силу в Японии и расширение производственных мощностей конкурентов, таких как TSMC, Western Digital, Micron и Kioxia. Samsung будет выпускать для AMD передовые 3-нм чипы с GAA-транзисторами

01.06.2024 [09:02],

Анжелла Марина

Компания Samsung объявила о расширении стратегического партнерства с американской компанией Advanced Micro Devices (AMD) в области разработки передовой 3-нанометровой технологии производства чипов. Используя более тесные связи с AMD, Samsung стремится обогнать своего главного конкурента, контрактного производителя полупроводников TSMC.

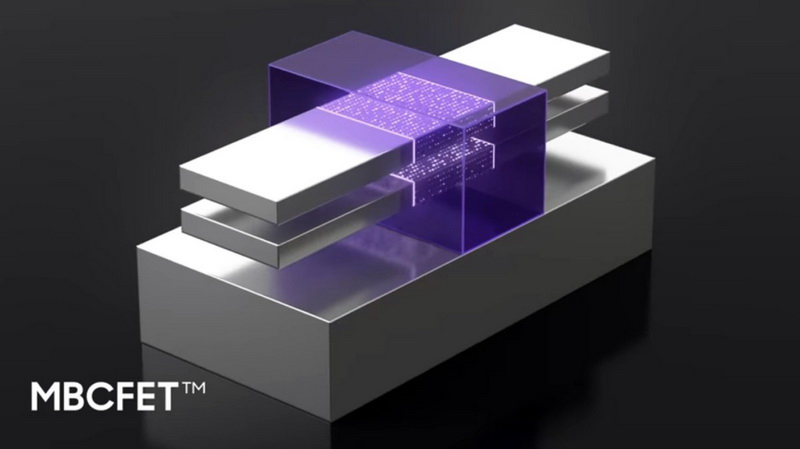

Источник изображения: Samsung Это партнерство позволит компаниям объединить усилия в разработке инновационных решений для производства чипов следующего поколения, которые будут использоваться в высокопроизводительных вычислительных системах, центрах обработки данных, смартфонах и других электронных устройствах. Как сообщает корейское новостное издание KED Globall, в рамках соглашения Samsung, крупнейший в мире производитель микросхем памяти, получит доступ к передовым разработкам AMD в области архитектуры чипов, а AMD, который в свою очередь разрабатывает микропроцессоры и графические процессоры, сможет воспользоваться мощностями Samsung по производству чипов с использованием новейшей 3-нм технологии транзисторов Gate-All-Around (GAA). Данная технология позволяет создавать чипы с рекордной плотностью транзисторов и улучшенными характеристиками производительности. По сравнению с предыдущим поколением 5-нм чипов, 3-нм чипы GAA обеспечивают прирост производительности на 30 %, снижение энергопотребления на 50 % и уменьшение площади чипа на 45 %. В настоящее время Samsung является единственным производителем в мире, который уже запустил 3-нм техпроцесс GAA в коммерческое производство, опередив основного конкурента тайваньскую компанию TSMC. Расширение сотрудничества с AMD позволит Samsung нарастить свою долю на рынке контрактного производства чипов и сократить отставание от TSMC. Известно, что в настоящее время Samsung контролирует около 17 % этого рынка, а TSMC — более 50 %. В дальнейшем Samsung планирует начать массовый выпуск 2-нм чипов на базе технологии GAA в 2025 году, что позволит ей упрочить лидерство в области полупроводниковых технологий. Apple представила 3-нм процессор M4 «с самым мощным NPU» в мире

07.05.2024 [18:27],

Николай Хижняк

В рамках мероприятия Let Loose компания Apple представила новый мобильный процессор M4, который послужит основой её продуктов нового поколения. Дебютировал он в составе новых флагманских планшетов iPad Pro с OLED-экраном.

Источник изображений: Apple Процессор Apple M4 с более чем 28 млрд транзисторов производится с использованием 3-нм техпроцесса TSMC второго поколения. В его состав входят 10 вычислительных ядер CPU (4 производительных и 6 энергоэффективных) и 10 графических ядер GPU на новой архитектуре с поддержкой динамической кеш-памяти, а также технологий сетчатого затенения и аппаратным ускорением трассировки лучей. Компания заявляет, что вычислительная производительность нового чипа до 50 % выше, а графическая до четырёх раз выше, чем у процессора M2. По словам Apple, новый процессор M4 также на 50 % энергоэффективное процессора M2. В рамках презентации также было заявлено, что M4 обеспечивает на фоне конкурентов такую же производительность, но при этом потребляет всего четверть от используемого ими питания. Никаких сравнительных графиков компания не привела. В составе Apple M4 также имеется новый 16-ядерный ИИ-движок (NPU) с производительностью 38 TOPS (триллионов операций в секунду). Он примерно в 60 раз быстрее NPU в составе процессора Apple A11 Bionic. Apple заявляет, что новый NPU в составе M4 быстрее любого другого NPU, который применяется в составе так называемых AI PC от конкурентов. В составе чипа также используется новый интерфейс дисплея с поддержкой частоты обновления до 120 Гц и технологии экрана Tandem OLED, которая применяется в новейшем планшете iPad Pro. Для Apple M4 заявляется пропускная способность унифицированной памяти на уровне 120 Гбайт/с. Развитие под санкциями: китайская SMIC разрабатывает технологии выпуска 3-нм чипов без EUV

22.12.2023 [18:50],

Сергей Сурабекянц

Несмотря на отсутствие доступа к оборудованию для выпуска чипов с литографией в экстремальном ультрафиолете (EUV) из-за санкций, китайская компания SMIC продолжает разработку 5-нм и 3-нм техпроцессов производства чипов. Ранее SMIC удалось наладить серийное производство 7-нм микросхем, опираясь исключительно на литографию в глубоком ультрафиолете (DUV), что само по себе не является невозможным — техпроцесс TSMC N7P также не использует EUV.

Источник изображения: SMIC В отчёте Nikkei утверждается, что сразу после запуска 7-нм техпроцесса 2-го поколения, SMIC создала исследовательскую группу для работы над 5-нм и 3-нм техпроцессами. Команду возглавляет ранее работавший в TSMC и Samsung содиректор SMIC Лян Монг-Сонг (Liang Mong-Song). «Нет более умного учёного или инженера, чем этот парень, — так охарактеризовал его Дик Терстон (Dick Thurston), бывший главный юрисконсульт TSMC. — Он действительно один из самых блестящих умов, которых я видел в области полупроводников». SMIC прошла долгий путь от небольшой полупроводниковой фабрики до пятого по величине контрактного производителя микросхем в мире. На фоне растущей напряжённости между США и Китаем компания была включена в санкционный список Министерства торговли США и потеряла доступ к передовым инструментам для обработки кремниевых пластин, что серьёзно замедлило её развитие и внедрение новых технологических процессов. На данный момент литографические машины ASML Twinscan NXT:2000i являются лучшими инструментами, которыми располагает SMIC — они могут производить травление с разрешением до 38 нм. Этот уровень точности обеспечивает экспонирование с шагом 38 нм с использованием двойной фотомаски, чего достаточно для производства чипов класса 7 нм. Согласно исследованиям ASML и IMEC, при 5 нм шаг металла уменьшается до 30-32 нм, а при 3 нм — до 21-24 нм, что уже требует применения EUV.

Источник изображения: ASML Но использование инструментов литографии со сверхвысоким разрешением (13 нм для EUV с низкой числовой апертурой) — не единственный путь к достижению сверхмалых размеров транзисторов. Другой вариант предусматривает нанесение нескольких последовательных масок, но это сложный процесс, который увеличивает продолжительность производственного цикла, снижает процент выхода годных изделий, увеличивает износ оборудования и повышает затраты. Однако без доступа к EUV-литографии у SMIC просто нет другого выбора, кроме как использовать тройное, четверное или даже пятикратное паттернирование. Терстон считает, что под руководством Лян Монг-Сонга SMIC сможет производить (если уже не производит) 5-нм чипы в больших количествах без использования инструментов EUV. Однако сегодняшний отчёт Nikkei впервые сообщает о возможной способности SMIC разработать в обозримом будущем 3-нм производственный процесс на оборудовании класса DUV. Intel впервые за 13 лет изменит транзисторы в чипах — компания показала RibbonFET и схему их обратного питания

20.09.2023 [11:15],

Геннадий Детинич

На конференции Innovation 2023 глава компании Intel Патрик Гелсингер (Patrick Gelsinger) показал кремниевую пластину с процессорами Arrow Lake, выполненными по техпроцессу 20A (20 ангстрем или 2 нм). Эти чипы появятся в 2024 году и станут первыми за 13 лет носителями новой архитектуры транзисторов. На мероприятии глава Intel раскрыл кое-какие детали будущих архитектур, что можно считать официальным подтверждением появившихся ранее утечек.

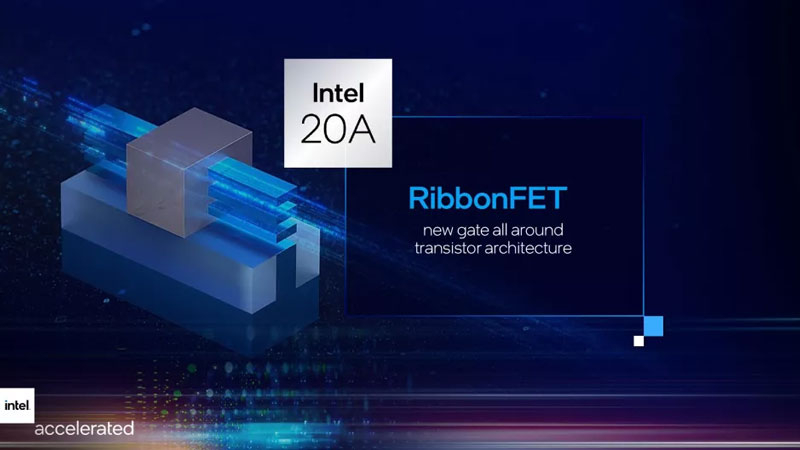

Источник изображения: Intel Значительным событием стало подтверждение планов Intel начать выпуск 2-нм процессоров в 2024 году — раньше, чем это сделают компании TSMC и Samsung, до этого показавшие значительный технологический отрыв от микропроцессорного гиганта. Компания Intel поставила перед собой цель освоить за четыре года выпуск процессоров на пяти новых технологических узлах и, похоже, строго следует этому плану. Более того, по ряду технологических новшеств Intel собирается оказаться впереди как Samsung, так и TSMC.

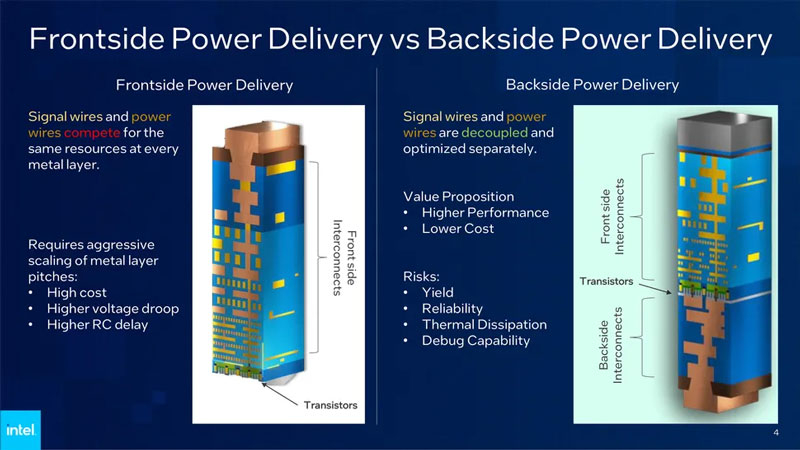

Пластина с чипами Arrow Lake В частности, компания Intel первой переведёт линии питания элементов процессоров на заднюю часть подложки. Сигнальные линии останутся на прежнем месте, а питание будет подаваться с обратной стороны непосредственно на транзисторы. Произойдёт это, начиная с транзисторов чипов Arrow Lake, которые компания уже выпускает в виде инженерных образцов. Разделение питания и сигнальных линий даст много преимуществ, хотя также будет сопряжено с технологическими трудностями. Разгрузка объёма пластины со стороны сигнального интерфейса позволит упростить разводку и повысить скорость работы сигнального интерфейса за счёт уменьшения длин соединений и, соответственно, снижения их сопротивления току. Такое же упрощение разводки питания (с обратной стороны) и даже увеличение сечения проводников питания позволит уменьшить переходные процессы и даже откроет путь к увеличению плотности размещения транзисторов. Компания TSMC, например, планирует внедрить похожую технологию не раньше 2026 года или на два года позже Intel.

Доставка питания сзади (справа на изображении). Слева — актуальный подход, когда сигнал и питание подаются в одном слое Но определённо революционным новшеством в процессорах Arrow Lake станут новые транзисторы RibbonFET Gate-All-Around (GAA) с каналами, полностью окружёнными затворами. Это будут первые с 2011 года новые транзисторы в процессорах Intel после начала производства транзисторов FinFET с вертикальными каналами (рёбрами), окружёнными затворами только с трёх сторон. Подобные транзисторы в собственной интерпретации (SF3E) уже выпускает компания Samsung, но она не готова сделать их массовыми. Компания Intel, похоже, готова организовать производство GAA-транзисторов на массовой основе. Архитектурно GAA-транзисторы Intel похожи на такие же транзисторы Samsung. Они точно также представлены расположенными друг над другом каналами в виде тонких нанолистов (наностраниц), окружённых затворами со всех сторон. В составе транзистора Intel использует четыре канала. По словам Intel, такая конструкция обеспечивает более быстрое переключение транзисторов при использовании управляющего тока аналогичного по силе току для FinFET. При этом GAA-транзистор занимает на подложке заметно меньше места, чем FinFET. Компания TSMC рассчитывает внедрить в производство собственную архитектуру GAA в 2025 году или на год позже Intel. В этом формально Samsung опередила своих конкурентов, но в плане массовости производства самых передовых решений она пока ничем похвастаться не может. Apple сэкономила миллиарды долларов на 3-нм процессорах благодаря эксклюзивной сделке с TSMC

07.08.2023 [22:15],

Николай Хижняк

Компания TSMC вышла на массовое производство 3-нм чипов с уровнем выхода годной продукции выше 70 %. И обычно клиенты оплачивают все пластины и чипы, включая бракованные. Однако на эксклюзивных условиях сотрудничества компания Apple платит тайваньскому контрактному производителю микросхем только за годные кристаллы, сообщает портал AppleInsider, ссылающийся на отчёт издания The Information.

Источник изображения: TSMC По словам операционного директора Apple Джеффа Уильямса (Jeff Williams), Apple и TSMC связывают долгие и насыщенные отношения. Как пишет The Information, эти отношения по-настоящему уникальны и выделяются как на фоне сотрудничества TSMC с другими своими клиентами, так и на фоне отношений прочих производителей чипов со своими покупателями. В частности, TSMC не взимает с Apple полную стоимость пластин с использованием 3-нм техпроцесса, в которых содержатся сотни кристаллов будущих процессоров. Тайваньский контрактный производитель берёт с Apple плату только за годные кристаллы. Обычно разница в цене не является статистически значимой, потому что со временем TSMC так или иначе выходит на уровень выпуска 99 % годных кристаллов на кремниевой пластине. Однако в настоящий момент уровень пригодных к использованию 3-нм кристаллов составляет около 70–80 %. Поскольку Apple не платит TSMC за негодные кристаллы, это позволяет ей значительно экономить. Речь идёт о миллиардах долларов. Apple выкупила практически все мощности TSMC для выпуска 3-нм изделий ещё несколько лет назад. The Information утверждает, что TSMC способна вести разработку новых технологических процессов в частности благодаря тому, что Apple готова заранее и в больших объёмах оплачивать производственные мощности для выпуска новых передовых чипов. Отмечается, что как только TSMC снизит уровень производственного брака кристаллов и повысит объём выпуска годных чипов, она сможет предоставлять свои услуги по производству 3-нм процессоров и другим компаниям, но уже без таких выгодных условий. Предполагается, что использование 3-нм процессоров в составе будущих смартфонах iPhone 15 до 35 % увеличит показатель их энергоэффективности по сравнению с актуальными моделями iPhone 14, сообщает AppleInsider. Один из первых 3-нм чипов производства Samsung обнаружился в ASIC-майнере

18.07.2023 [23:34],

Николай Хижняк

Хотя Samsung начала массовое производство чипов на базе техпроцесса SF3E (3 нм, транзисторы GAA) примерно год назад, к настоящему моменту мало кто из производителей электроники подтвердил его использование в своих продуктах. Недавно аналитики TechInsights выяснили, что одним из первых заказчиков 3-нм чипов у Samsung стала компания MicroBT, выпускающая ASIC-майнеры. Выполненный по технологии SF3E чип применяется в её криптомайнере Whatsminer M56S++.

Источник изображения: Arm Специализированные интегральные схемы ASIC для добычи криптовалюты представляют собой небольшие чипы с относительно малым количеством входящих в их состав транзисторов и повторяющимися логическими структурами, похожими на простые битовые ячейки памяти SRAM. В целом за счёт простоты производства таких чипов это делает их весьма подходящей платформой для тестирования передовых технологически процессов. Поэтому совсем неудивительно, что техпроцесс SF3E нашёл своё первое практическое применение именно в среде криптомайнинга. К сожалению, в открытом доступе о ASIC-майнере Whatsminer M56S++ не так много информации. Известно лишь, что система компании MictoBT на основе этого чипа обеспечивает хешрейт на уровне 240–256 Тхеш/с и обладает энергоэффективностью 22 джоуля на терахэш. На данный момент неизвестно, используется ли 3-нм технология SF3E компании Samsung в каких-либо других коммерческих решениях помимо оборудования для майнига. Однако сама Samsung заявляет, что «использует этот техпроцесс в своих продуктах». «Мы массово производим чипы на основе первого поколения 3-нм техпроцесса со стабильным уровнем выхода годных микросхем. С учётом этого опыта мы уже ведём разработку второго поколения техпроцесса, который обеспечит ещё более высокий выход годных чипов», — цитирует портал Tom’s Hardware одно из недавних заявлений компании. По сравнению с техпроцессами 5-нм класса Samsung второго поколения (SF5, 5LPP), SF3E обещает снижение энергопотребления микросхем до 45 % при сохранении той же частоты работы, либо повышение производительности до 23 % при сохранении количества транзисторов и мощности. Кроме того, чипы с использованием SF3E занимают на 16 % меньшую площадь. Intel представила недорогой и энергоэффективный 16-нм техпроцесс для широкого спектра чипов

12.07.2023 [16:44],

Николай Хижняк

Контрактный производитель полупроводников Intel Foundry Services (IFS) представил новый технологический процесс 16-нм класса, получивший название Intel 16. Он предназначен для производства чипов для мобильных устройств, RF-модулей, компонентов IoT, бытовой техники, устройств для хранения данных, а также для использования в военной и аэрокосмических отраслях. Новая технология дополняет 22-нм техпроцесс Intel FFL и считается недорогим техпроцессом на основе FinFET.

Источник изображения: Intel Как указывается в пресс-релизе компаний Synopsys, Cadence Digital и Ansys, являющихся ведущими поставщиками средств автоматизации проектирования электроники, новый техпроцесс Intel 16 разработан специально под широкий круг изделий от разных заказчиков. Технология класса 16 нм Intel предлагает более высокую плотность транзисторов, более высокую производительность и энергоэффективность по сравнению с планарными техпроцессами, которые применяются сегодня для перечисленных выше полупроводниковых изделий, а также обещает упросить процесс проектирования и производства полупроводниковых компонентов. Сотни различных видов электронных микросхем по-прежнему производятся с применением зрелых технологических узлов. Сюда можно отнести однопрограммные процессоры, различные контроллеры и аналоговые устройства, чипы для бытовой техники и радиоустройств. Использование зрелых узлов обходится дешевле, проще и сопровождается меньшим количеством брака. Хотя для передовых вычислений вроде ИИ используются большие и мощные чипы вроде AMD Instinct MI300 и NVIDIA H100, которые выпускаются по самым передовым техпроцессам, но всё равно эти сферы не обходятся без более компактных и простых чипов, обеспечивающие меньший уровень производительности, но при этом обладающие значительно более высокими показателями энергоэффективности. Исходя из этого производители чипов по-прежнему предлагают своим клиентам продукты на основе недорогих зрелых технологических процессов, в которых применяются транзисторы FinFET. Например, та же компания TSMC в этом случае предлагает использовать её техпроцесс N12e. Компании Ansys, Cadence и Synopsys сообщили, что уже внедрили поддержку технологического процесса Intel 16 в своих программных продуктах для автоматизации проектирования микросхем. Та же Cadence, например, адаптировала применение Intel 16 для проектирования компонентов PCIe 5.0, своего мультипротокольного решения 25G PHY, мультипротокольных решений для потребительских продуктов с поддержкой стандартов PCIe 3.0 и USB 3.2, для различных компонентов памяти LPDDR5/4/4X, а также интерфейсов MIPI D-PHY v1.2 для камер и цифровых дисплеев. В свою очередь Synopsys предлагает поддержку Intel 16 в составе набора инструментов Synopsys.ai с поддержкой ИИ для более быстрого внедрения чипов. Разработчики полупроводниковых микросхем, не имеющие собственных производств, уже могут начать использовать инструменты проектирования, моделирования и проверки своих решений на основе техпроцесса Intel 16. TSMC ускорила разработку 2-нм техпроцесса — тестовое производство хотят запустить в этом году

05.06.2023 [19:59],

Николай Хижняк

Тайваньский контрактный производитель микросхем TSMC ускорил разработку 2-нм технологического процесса из-за высокого потенциального спроса на эту продукцию со стороны таких компаний, как NVIDIA и Apple. Об этом сообщает тайваньское издание Economic Daily.

Источник изображения: TSMC По словам издания, тайваньская компания уже приступила к подготовке к старту мелкосерийного производства 2-нм чипов, а массовое производство микросхем этого класса должно начаться к 2025 году. Со ссылкой на источники Economic Daily сообщает, что в рамках подготовки к тестовому производству микросхем класса 2-нм TSMC передислоцировала инженеров и поддерживающий персонал в центр разработки, расположенный в городском округе Баошань. В рамках тестового производства до конца этого года планируется выпуск 1000 кремниевых пластин, говорится в сообщении одного из источников, на 2024 год компания запланировала ещё один пробный выпуск пластин, а старт массового производства чипов согласно нормам 2 нм должен начаться в 2025 году. Для массового производства 2-нм микросхем компания расширит мощности на своей фабрике в Баошани, а также задействует новый завод в Тайчжуне, что на западе Тайваня. Для TSMC важно начать тестовое производство 2-нм чипов как можно скорее, так как на этой фазе производства не исключено возникновение технических сложностей, для решения которых потребуется время. Это будет первое поколение чипов компании, в которых будут применяться транзисторы GAA с круговым затвором. По данным источников тайваньского издания, разработка 2-нм техпроцесса TSMC пока идёт хорошо. Отмечается, что конкуренция среди клиентов компании за использование нового техпроцесса стала более интенсивной, что может говорить о высоком уровне инвестиций в разработку и развитие индивидуальных решений. По словам тех же источников, TSMC активно использует в разработке нового техпроцесса алгоритмы искусственного интеллекта, за счёт которых производитель пытается повысить энергоэффективность новых чипов и, вероятно, снизить воздействие их производства на окружающую среду. Тайваньская компания использует ИИ-платформу AutoDMP от NVIDIA, которая позволяет 30-кратно ускорить процессы оптимизации проектирования кристаллов по сравнению с предыдущими методами и технологиями. Средство проектирования чипов от NVIDIA призвано сделать производство дешевле, а сами чипы — производительнее и энергоэффективнее. |