|

Опрос

|

реклама

Быстрый переход

Intel: Panther Lake возьмут всё лучшее от актуальных Core и ангстремного техпроцесса 18A, но выйдут в 2026 году

02.04.2025 [04:34],

Анжелла Марина

На конференции Intel Vision в Лас-Вегасе компания рассказала о грядущих процессорах Panther Lake, производство которых начнётся в конце этого года, а на рынке они появятся в начале следующего. По словам руководства компании, новые чипы объединят лучшие черты предыдущих поколений Lunar Lake и Arrow Lake — энергоэффективность и производительность, а также станут первым продуктом на новом производственном техпроцессе Intel 18A.

Источник изображения: Intel Panther Lake станет не просто очередной новинкой в линейке процессоров. Они станут первыми чипами, выпущенными по передовому техпроцессу 18A. Этот технологический шаг, как пишет PCWorld, был заложен ещё при прежнем главе компании Патрике Гелсингере (Patrik Gelsinger), который поставил цель внедрить пять технологических процессов за четыре года. Хотя Гелсингер ушёл с поста, достижение этой цели станет частью его наследия. Джим Джонсон (Jim Johnson), старший вице-президент клиентского подразделения Intel, подчеркнул, что Panther Lake сочетает в себе энергоэффективность Lunar Lake и производительность Arrow Lake. «Я лично в восторге от Panther Lake, потому что он объединяет лучшее от наших прошлых архитектур, рассчитан на масштабируемый 18A и готов к выпуску уже в этом году», — заявил он. На данный момент компания вышла на стадию опытного производства с 18A и готовит масштабирование производства для полноценного серийного выпуска.

Источник изображения: Mark Hachman / IDG Технические детали Panther Lake, скорее всего, будут раскрыты ближе к выставке Computex, которая пройдёт в конце мая, а в 2026 году Intel выпустит следующий флагманский чип Nova Lake, о чём сообщил новый генеральный директор компании Лип-Бу Тан (Lip-Bu Tan) в письме акционерам. В рамках Intel Vision был показан слайд, на котором Panther Lake указан как продукт 2026 года. Предполагается, что производство новых чипов действительно начнётся в 2025 году, однако массовый выход на рынок задержится до начала 2026-го.

Источник изображения: Intel Стоит отметить, что Intel активно инвестирует в развитие искусственного интеллекта (ИИ), привлекая разработчиков к своей платформе. В рамках этого направления компания запустила AI Showcase – витрину приложений с оптимизированными под её процессоры решениями. Также представлено новое приложение AI Playground, которое позволит пользователям запускать ИИ-модели и создавать с их помощью произведения искусства прямо на своих ПК. Что касается приоритетов Intel на 2025 год, то компания обозначила три направления, два из которых касаются внедрения искусственного интеллекта в пользовательские компьютеры, рабочие станции и автомобили. Третья задача связана с дальнейшим развитием ИИ-инфраструктуры, обеспечивающим совместимость аппаратного и программного обеспечения, снижение энергопотребления и стоимости для будущих поколений своих продуктов. Imec получит лучшие инструменты ASML для разработки техпроцессов тоньше 2 нм

12.03.2025 [20:45],

Геннадий Детинич

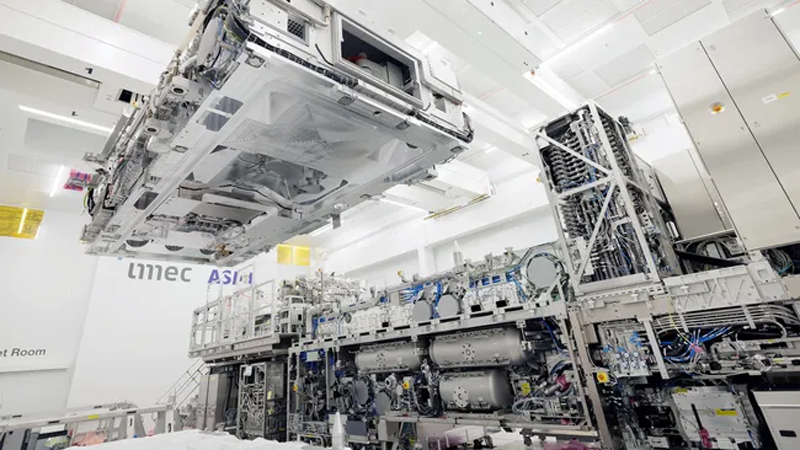

На днях бельгийский исследовательский центр Imec и компания ASML заключили пятилетнее соглашение, в рамках которого нидерландский производитель литографического оборудования предоставит Imec полный комплект самых современных инструментов для выпуска чипов и проверки качества продукции. Партнёрство позволит разработать и внедрить в промышленность техпроцессы с нормами менее 2 нм вплоть до атомарного уровня.

Источник изображения: Imec Ранее исследователи Imec пользовались передовым литографическим оборудованием на родной площадке ASML в Вельдховене, Нидерланды. Подписанное соглашение позволит разместить аналогичное оборудование на площадке Imec, что облегчит и упростит работу сотрудникам центра и их партнёрам из академических и коммерческих кругов. Новейшее оборудование от ASML, включая сканер EUV с высоким значением числовой апертуры (High-NA) стоимостью $350 млн, будет интегрировано в пилотную линию NanoIC по обработке кремниевых пластин в Бельгии. Ранее в линию NanoIC вложились ЕС и власти Фландрии. Собственно, поставка ASML во многом будет оплачена за счёт финансирования из европейских фондов и программ, направленных на разработку передовых полупроводниковых технологий. Вместе со сканером Twinscan EXE (High-NA 0,55) в Imec будут доставлены сканер Twinscan NXE (NA 0,33), Twinscan NXT (DUV, 193 нм), оптические метрологические инструменты ASML YieldStar и одно- и многолучевые инспекционные инструменты HMI. Бельгийцы получат все лучшие «игрушки» ASML, а взамен передадут для внедрения в промышленность технологии литографического производства с технологическими нормами менее 2 нм и будут разрабатывать техпроцессы двух следующих десятилетий. Отличным дополнением к совместной работе над технологическими узлами следующего поколения для логических микросхем с техпроцессом менее 2 нм, станет сотрудничество в области технологий производства DRAM, кремниевой фотоники и передовых решений для упаковки чипов — всего того, что крайне востребовано современной полупроводниковой промышленностью, явно подошедшей к технологическому барьеру классических техпроцессов. Micron первой начала поставлять чипы DDR5, выпущенные по техпроцессу 1γ с EUV-литографией — быстрые, холодные и плотные

26.02.2025 [09:54],

Геннадий Детинич

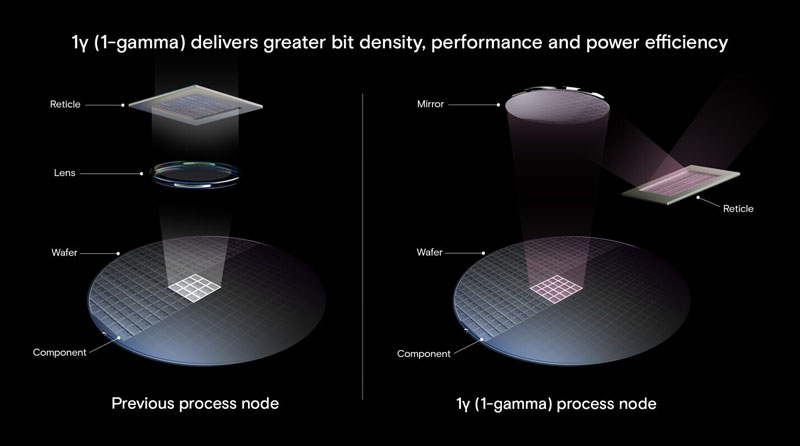

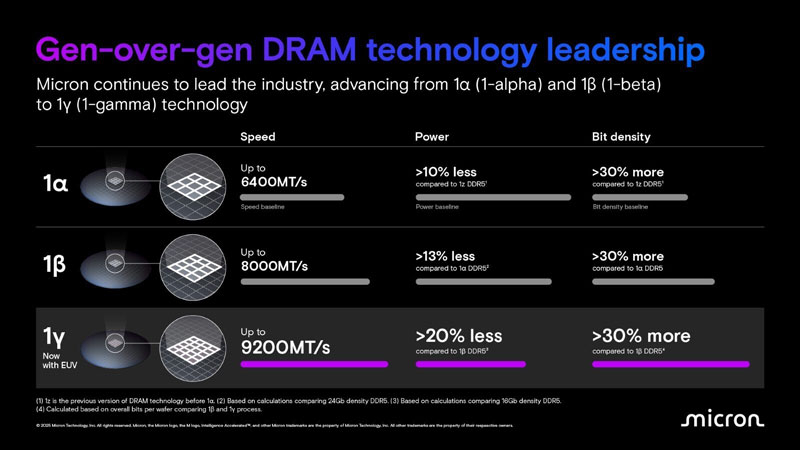

Компания Micron Technology объявила, что первой в отрасли начала поставки чипов памяти DDR5, изготовленных с использованием полупроводниковой EUV-литографии. Память поставляется избранным партнёрам для оценки эффективности самых передовых на сегодня решений. Новые чипы обладают повышенной пропускной способностью, пониженным энергопотреблением и более плотным размещением ячеек — всем, что нужно для развития ИИ, от гаджетов до серверов.

Источник изображений: Micron Новая память Micron продолжает относиться к классу 10-нм продукции. Нет точной информации, насколько цифра техпроцесса близка к 10 нм. Но это уже третье приближение к ней и, что более важно, компания наконец-то перешла к использованию литографических сканеров в экстремальном ультрафиолетовом диапазоне с длиной волны 13,5 нм (EUV). Дальше масштабирование пойдёт легче.  Если верить Micron, избранным партнёрам начали отгружаться 16-Гбит чипы DDR5. Кристаллы памяти выпущены с использованием техпроцесса 1γ (гамма). Предыдущие техпроцессы этого класса — 1α (альфа) и 1β (бета) — реализовывались с использованием сканеров с длиной волны 193 нм. Рассказывая о преимуществах чипов поколения 1γ, компания сравнивает их с чипами DDR5 предыдущего поколения — 1β. По сравнению с ними новинки на 15 % быстрее (до 9200 МТ/с), потребляют более чем на 20 % меньше энергии и обладают на 30 % большей плотностью расположения ячеек на кристалле.  Улучшенные характеристики памяти будут востребованы в периферийных устройствах с поддержкой искусственного интеллекта, в ПК с ИИ-функциями и в серверах, на которых работают большие языковые модели. Тем самым ассортимент памяти с технологическими нормами 1γ не ограничится лишь производством чипов DDR5, но также будет расширен за счёт выпуска других типов памяти, например LPDDR5X. Intel отложила запуск Xeon нового поколения и отменила ускорители Falcon Shores, но потребительские Panther Lake выйдут вовремя

31.01.2025 [18:19],

Сергей Сурабекянц

Компания Intel в рамках квартальной отчётной конференции сообщила о переносе начала поставок процессоров Xeon Clearwater Forest для центров обработки данных на первую половину 2026 года. Также компания заявила, что ИИ-ускорители Falcon Shores не будут выпущены на рынок, а послужат для тестов при разработке преемника под кодовым названием Jaguar Shores. В то же время Intel подтвердила, что поставки чипов Panther Lake для клиентских ПК начнутся по плану во второй половине 2025 года.  Задержка выпуска ключевого серверного процессора с кодовым названием Clearwater Forest произошла на фоне раскрытия компанией удручающих финансовых результатов за четвёртый квартал 2024 года и весь год в целом. В сочетании с объявленной Intel отменой ускорителей Falcon Shores, конкурентная позиция Intel на стремительно растущем рынке ИИ ослабла ещё сильнее. В настоящее время Intel наращивает производство своих энергоэффективных процессоров Xeon 6 Sierra Forest и высокопроизводительных процессоров Xeon 6 Granite Rapids. Компания рассчитывает, что эти процессоры помогут в стабилизации её доли рынка в этом году. Выход в дальнейшем процессоров следующего поколения Xeon 7 Clearwater Forest и Xeon 7 Diamond Rapids должен, по планам Intel, переломить ход событий и вернуть компании потерянную долю рынка. «Мы также добиваемся хорошего прогресса в работе над Clearwater Forest, нашим первым серверным продуктом на Intel 18A, который мы планируем выпустить в первой половине следующего года», — сказала временно исполняющая обязанности соруководителя Intel Мишель Джонстон Холтхаус (Michelle Johnston Holthaus). Она подтвердила возникшие трудности с технологией упаковки Clearwater Forest, заверив при этом, что внедрение техпроцесса 18A идёт по плану.

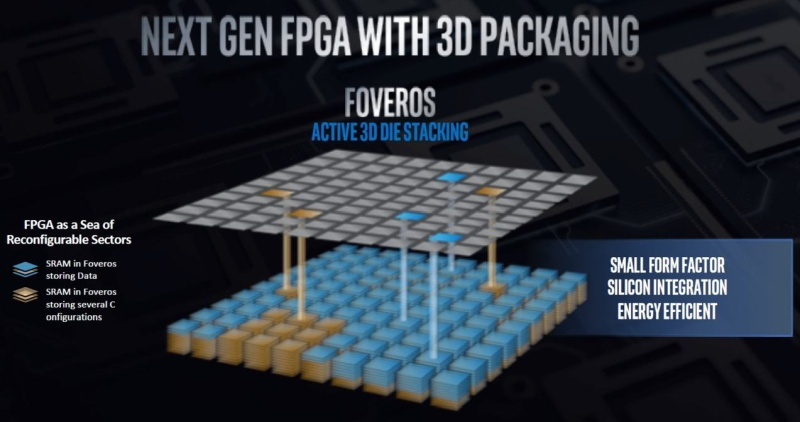

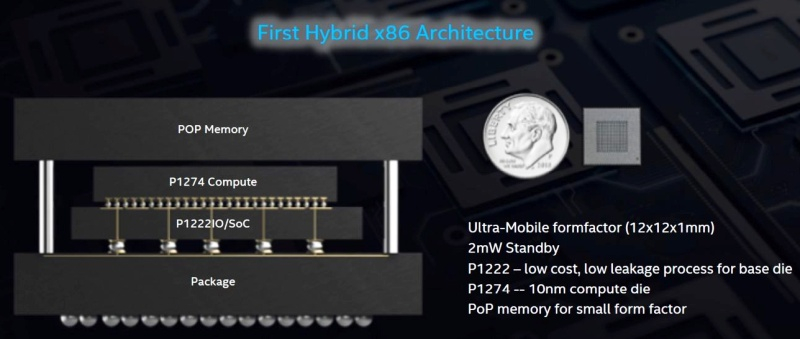

Источник изображений: Intel Clearwater Forest много значит для Intel, поскольку это первый процессор для центров обработки данных с вычислительными чиплетами, произведёнными по техпроцессу Intel 18A (класс 1,8 нм) и упакованный по технологии Foveros 3D. Если компания сможет добиться массового и экономически эффективного выпуска Clearwater Forest, это станет серьёзным свидетельством успеха 18A, что может привлечь потенциальных клиентов к контрактному производству Intel Foundry.  На данный момент Intel с оптимизмом смотрит на 18A. «18A — это область хорошего прогресса, — уверен финансовый директор Intel Дэвид Цинснер (David Zinsner). — Как и в любом новом процессе, на этом пути были взлёты и падения, но в целом мы уверены, что обеспечиваем конкурентоспособный процесс». Что касается графического процессора Falcon Shores, рассчитанного на рабочие нагрузки ИИ, представитель Intel посоветовал аналитикам и инвесторам умерить свои ожидания, поскольку Falcon Shores в основном будет служить тестовым чипом при разработке аппаратной и программной экосистемы следующих поколений гибридных процессоров, в частности, для своего преемника под кодовым названием Jaguar Shores. Принять такое решение компания была вынуждена в результате провала процессора Intel Gaudi 3, который не смог составить конкуренцию решениям AMD и Nvidia. В этой ситуации запуск в коммерческую эксплуатацию ещё одного неудачного продукта потенциально может похоронить репутацию компании.  «Многие из вас слышали, как я умерила ожидания в отношении Falcon Shores в прошлом месяце, — заметила Хольтхаус во время отчёта о доходах компании в четверг. — Основываясь на отзывах отрасли, мы решили использовать Falcon Shores в качестве внутреннего тестового чипа. Не выводя его на рынок, мы поддержим наши усилия по разработке системного решения в масштабе стойки с Jaguar Shores для более широкого охвата центра обработки данных ИИ». Falcon Shores — первый графический процессор Intel с многочиплетной конструкцией, основанный на ядрах Xe-HPC или Xe3-HPC. Он предназначен для обслуживания высокопараллельных рабочих нагрузок ИИ и высокопроизводительных вычислений. Продукт должен значительно повысить производительность и энергоэффективность, хотя компания воздержалась от предоставления фактических цифр.  Задержка с выпуском процессоров Clearwater Forest и отмена массового производства графических ускорителей Falcon Shores может очень дорого обойтись Intel, которая испытывает серьёзнейшие трудности и продолжает терять доверие инвесторов. США запустили расследование зависимости от олдскульных китайских чипов

23.12.2024 [18:28],

Сергей Сурабекянц

В понедельник Белый дом инициировал новое расследование в отношении китайских полупроводников, выполненных по старым техпроцессам, которые широко используются везде: от автомобилей и умного дома до оборонных систем. По мнению администрации США, Китай «регулярно применяет нерыночную политику и практику», что позволяет китайским компаниям «существенно вредить конкуренции и создавать опасные зависимости в цепочке поставок в основных полупроводниках»

Источник изображения: unsplash.com Новое расследование должно оценить зависимость США от китайских чипов, изготовленных по зрелым техпроцессам, в широком спектре технологических областей: от телекоммуникаций до электросетей. Так называемое расследование по разделу 301 будет так же изучать, по словам представителя администрации США, «действия, политику и практику Китая по производству подложек из карбида кремния или других пластин, используемых в качестве исходных материалов для производства полупроводников». Так называемые устаревшие чипы производятся с использованием менее передовых технологий производства. Китайские производители чипов по-прежнему отстают на несколько поколений от лидеров отрасли, таких как TSMC, но они способны производить устаревшие чипы в больших количествах. Расследование проводится в соответствии с Законом о торговле 1974 года. Одним из потенциальных средств правовой защиты, в соответствии с этим законом, является введение пошлин на рассматриваемую продукцию. Администрация США последовательно оказывает санкционное давление на технологический сектор Китая. Новое расследование знаменует собой эскалацию давления на полупроводниковую промышленность Китая. До сегодняшнего дня большинство действий, предпринятых США, были связаны с передовыми чипами, в частности с применяемыми в бурно развивающемся секторе искусственного интеллекта. Найден рецепт продления закона Мура: кремний «приправили» графеном и запекли при 300 °C

12.12.2024 [14:47],

Геннадий Детинич

Уменьшение техпроцессов для производства чипов почти достигло физических ограничений. Отлично показавшая себя в качестве разводки между транзисторами медь при дальнейшем уменьшении сечения проводов начала оказывать току растущее сопротивление. Потенциально её можно заменить графеном. Проблема в том, что современные технологии нанесения графена на чипы несовместимы с КМОП-процессами, применяемыми для массового выпуска чипов. Возможно, решение этой проблемы найдено.

Источник изображения: ИИ-генерация Кандинский 3.1/3DNews Предложенные ранее технологии осаждения углерода на микросхемы (транзисторы) для создания графеновых проводящих линий предполагают использование высоких температур — от 400 °C и выше. Такие температуры губительны для кремниевых транзисторов, изготовленных с применением КМОП-технологий. Необходим иной способ нанесения графена на чип, и такой способ придумали в американской компании Destination 2D. Стоит отметить, что научным консультантом Destination 2D является Константин Новосёлов — один из лауреатов Нобелевской премии по физике за 2010 год и соавтор исследования, приведшего к открытию графена в 2004 году. Предложенная компанией Destination 2D технология нанесения графена на чипы осуществляется в газовой среде под давлением от 410 до 550 кПа. Осаждение происходит не на «голый» чип, а на предварительно нанесённую на кристалл плёнку никеля. Никель выполняет роль расходного материала и впоследствии удаляется с поверхности кристалла. Внесение этого этапа в техпроцесс позволило снизить температуру осаждения графена до приемлемых для КМОП 300 °C. При такой температуре транзисторные структуры на кристалле не разрушаются, а рисунок соединений формируется с использованием графена. Также исследователи из Destination 2D решили проблему повышения проводящих свойств графена. Утверждается, что предложенный компанией особый метод легирования графена — методом интеркаляции — делает его в 100 раз более проводящим, чем медь. Это позволяет сохранить и даже увеличить плотность тока по мере уменьшения размеров транзисторов, а значит, остаётся возможность повышать плотность их размещения на кристалле. Более того, разработчики утверждают, что благодаря интеркаляции проводимость графена увеличивается по мере уменьшения размеров элементов, что даёт шанс продлить действие закона Мура ещё на несколько лет. Руководство Destination 2D верит, что пройдёт немного времени, и предложенный ими графеновый техпроцесс будет внедрён в производство передовых микросхем. Компания активно сотрудничает с рядом производителей чипов, чтобы приблизить этот момент. Intel достигла низкой плотности дефектов для техпроцесса 18A

05.09.2024 [04:27],

Анжелла Марина

На технологической конференции Deutsche Bank 2024 Intel раскрыла информацию о плотности дефектов своего передового техпроцесса 18A (1,8 нм). По словам компании, этот показатель свидетельствует о «здоровом» состоянии технологии и высоком уровне надёжности производственного процесса. Количество потенциальных заказчиков, заинтересованных в использовании 18A, растёт.

Источник изображения: Tom's Hardware Несмотря на недавнюю новость о неудачных тестах, произведённых одним из ключевых игроков в сфере сетевого оборудования и радиочипов компанией Broadcom, Intel утверждает, что количество клиентов, заинтересованных в использовании этой технологии, продолжает расти. По словам генерального директора компании Пэта Гелсингера (Pat Gelsinger), плотность дефектов (D0) уже снизилась до уровня ниже 0,4 дефекта на квадратный сантиметр. «Я рад сообщить, что для этого производственного процесса мы сейчас находимся ниже уровня плотности дефектов 0,4 d0, что свидетельствует о здоровом состоянии процесса», — заявил Гелсингер. В индустрии считается, что значение D0 ниже 0.5 дефекта на квадратный сантиметр (0,5 def/cm²) — это хороший показатель. А с учётом того, что до начала массового производства 18A остаётся ещё несколько кварталов, ожидается, что к этому моменту плотность дефектов станет ещё ниже. Для сравнения, плотность дефектов техпроцессов N7 и N5 тайваньской компании TSMC за три квартала до начала массового производства составляла около 0,33 дефекта на квадратный сантиметр, что примерно соответствует текущему состоянию 18A. При запуске массового производства N5 показатель D0 достиг 0,1 дефекта на квадратный сантиметр. Хотя плотность дефектов N3 на старте массового производства была выше, чем у N5, через пять-шесть кварталов она сравнялась с показателем N5, демонстрируя схожую динамику улучшения. Как сообщает Tom's Hardware, Intel планирует использовать 18A для производства собственных процессоров Panther Lake для персональных компьютеров и Clearwater Forest для дата-центров. Также на этом техпроцессе будет выпускаться процессор Diamond Rapids. Несколько недель назад Intel объявила о выпуске комплекта для разработки продуктов (PDK) версии 1.0 для 18A, что позволит как собственным разработчикам компании, так и её клиентам начать или завершить проектирование чипов на базе 18A. Среди заказчиков интерес к 18A проявили компания Microsoft, которая планирует использовать его для производства своих процессоров, и Министерство обороны США. «Сейчас у нас более десятка клиентов активно работают с нашим комплектом разработки 18A (PDK 1.0)», — сообщил Гелсингер. В общей сложности Intel ожидает запуска в производство восьми продуктов на базе 18A к середине 2025 года. Передовой 1,8-нм техпроцесс Intel 18A не готов к массовому производству, показали тесты Broadcom

04.09.2024 [19:14],

Анжелла Марина

Intel столкнулась с неприятным сюрпризом в рамках своего проекта по развитию контрактного производства чипов, который был запущен в 2021 году. Тесты компании Broadcom показали, что передовой технологический процесс Intel 18A не готов к массовому производству.

Источник изображения: Intel По информации Reuters, испытания передового производственного процесса Intel 18A, проведённые одним из ключевых игроков в сфере сетевого оборудования и радиочипов, компанией Broadcom, оказались неудачными. Broadcom получила от Intel кремниевые пластины с полупроводниками, выполненными по технологии Intel 18A. Но после изучения этих пластин инженеры и руководство Broadcom пришли к выводу, что процесс 18A пока не готов к массовому производству. Неудачные тесты Broadcom нанесли удар по планам Intel по развитию контрактного производства чипов, так как Intel, под руководством нового генерального директора Пэта Гелсингера (Pat Gelsinger), рассматривает контрактное производство как ключевой элемент стратегии по восстановлению своих позиций. Компания вложила около $100 млрд в расширение производственных мощностей на территории США и рассчитывает привлечь крупных контрактных клиентов, таких как Nvidia или Apple, чтобы заполнить эти мощности. Однако, несмотря на заявления представителя Intel о том, что с технологией 18A всё в порядке, и о наличии «большого интереса со стороны отрасли», компания Broadcom пока не готова делать окончательные выводы о сотрудничестве. «Мы оцениваем все предложения Intel Foundry и ещё не завершили эту оценку», — заявил представитель Broadcom. Ситуация осложняется текущими финансовыми трудностями Intel. Во втором квартале компания зафиксировала операционные убытки в подразделении Foundry в размере $7 млрд, что превышает убытки прошлого года в $5,2 млрд, а руководство Intel прогнозирует выход на безубыточность в этом бизнесе только к 2027 году. В условиях падения рыночной капитализации и сокращения инвестиций в строительство новых производств, неудача с Broadcom может ещё больше осложнить ситуацию, тем более на фоне сокращения 15 % рабочих мест и пересмотре капитальных затрат. В середине сентября совет директоров компании рассмотрит ещё один план по сокращению расходов в отдельных бизнес-подразделениях. Что касается компании Broadcom, она хоть и не столь известна широкой публике, является крупным производителем сетевого оборудования и радиочипов, её выручка от продаж чипов в прошлом финансовом году составила $28 млрд. Компания активно участвует в проектах, связанных с искусственным интеллектом, а аналитик J.P. Morgan Харлан Сур (Harlan Sur) прогнозирует, что в этом году её доходы от ИИ составят 11-12 миллиардов долларов, по сравнению с $4 млрд в прошлом году. Интересно, что Broadcom сотрудничает с Google (Alphabet) и Meta✴ Platforms в производстве их собственных процессоров для ИИ, что может включать в себя заключение контрактов с производителями, в том числе с Intel или TSMC. Несмотря на трудности, Intel продолжает продвигать свой техпроцесс 18A. Компания выпустила набор инструментов для других производителей чипов и, по словам Гелсингера, около десятка клиентов уже активно изучают его. Intel планирует завершить подготовку производства к концу года и начать серийный выпуск чипов в 2025 году. Однако, ситуация с Broadcom показывает, что переход на новую технологию сопряжён с рисками и может отпугнуть потенциальных клиентов, особенно учитывая стоимость производства на передовых технологических узлах, которая исчисляется несколькими десятками тысяч долларов только за одну пластину. Чиплеты AMD с ядрами Zen 5 содержат 8,315 млрд транзисторов — плотность выросла на 28 %

18.07.2024 [19:53],

Николай Хижняк

В конце июля компания AMD выпустит две серии процессоров — настольные Ryzen 9000 (Granite Ridge) и мобильные Ryzen AI 300 (Strix Point) — на базе новейшей архитектуры Zen 5. Портал HardwareLuxx.de выяснил недостающие подробности об этих процессорах. В частности, стали известны размеры кристаллов данных чипов и количество используемых в них транзисторов.

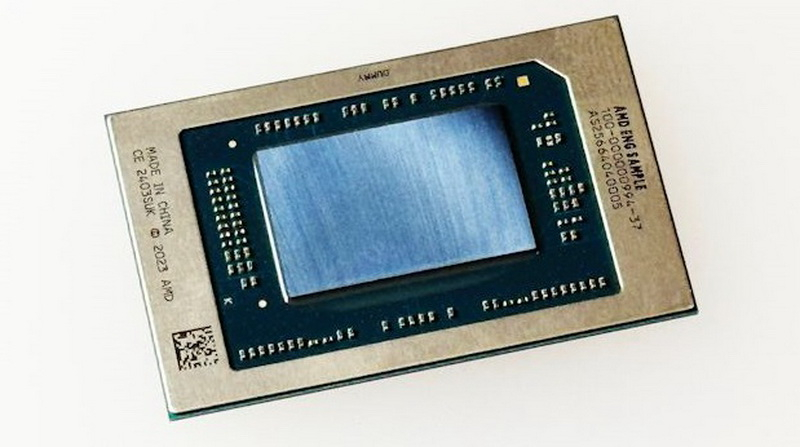

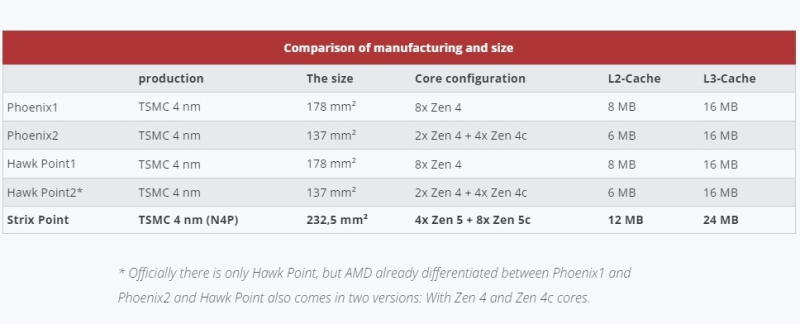

Источник изображения: AMD Процессоры Ryzen AI 300 (Strix Point) построены на монолитном кристалле, который производится с использованием 4-нм техпроцесса N4P компании TSMC. Это немного улучшенная версия техпроцесса N4, на базе которого выпускаются процессоры AMD Phoenix и Hawk Point на архитектуре Zen 4. Площадь кристалла Strix Point составляет 232,5 мм2. Таким образом, он значительно больше кристаллов Hawk Point и Phoenix с площадью 178 мм2.

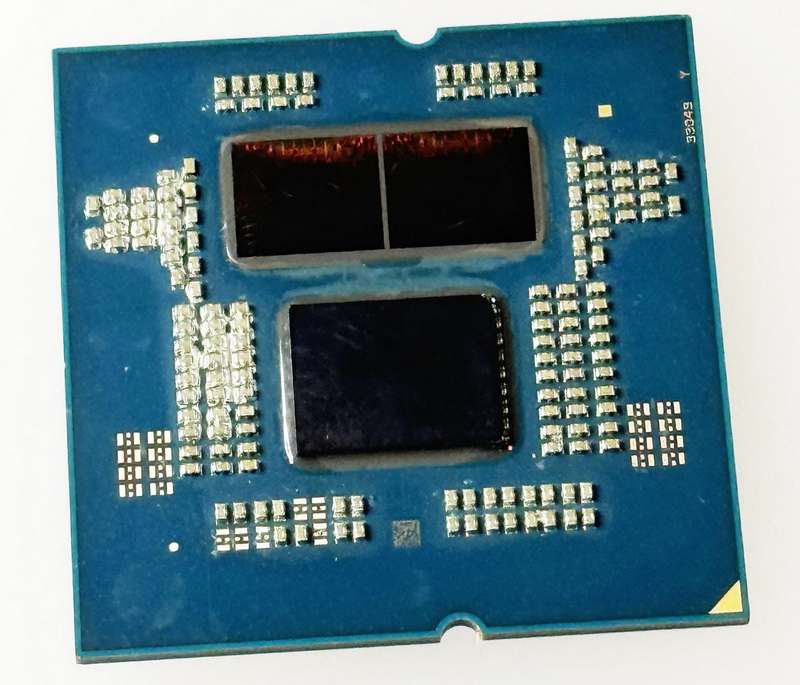

Источник изображения: HardwareLuxx.de Выросшая площадь кристалла Strix Point объясняется увеличившимся количеством исполнительных блоков встроенной графики Radeon 800M на новой архитектуре RDNA 3.5 с 8 до 12 у модели Ryzen AI 9 365 и с 12 до 16 у Ryzen AI 9 HX 370. Также площадь нового кристалла стала больше из-за увеличившегося до 24 Мбайт объёма кеш-памяти L3 и в целом из-за более крупных ядер Zen 5 и Zen 5c. Настольные процессоры Ryzen 9000 (Granite Ridge) используют чиплетную компоновку, как у Ryzen 7000 (Raphael). AMD подтвердила, что в новых процессорах используется блок ввода-вывода I/O die (cIOD) от Raphael, производящийся с использованием того же 6-нм техпроцесса. Площадь этого кристалла не изменилась и составляет 122 мм2. В нём содержатся 3,4 млрд транзисторов. Для сравнения, cIOD процессоров Ryzen 5000 (Vermeer) и Ryzen 3000 (Matisse) производились с применением 12-нм техпроцесса компании Global Foundries и обладали площадью 125 мм2, но содержали значительно меньшее количество транзисторов — 2,09 млрд. Ключевым фактором увеличения площади кристалла cIOD стал встроенный в него блок iGPU с двумя исполнительными блоками.  В процессорах Ryzen 9000 используется новый кристалл CCD с восемью вычислительными ядрами, получивший название Eldora. По данным HardwareLuxx.de, он производится на базе того же 4-нм техпроцесса N4P, что и кристаллы процессоров Strix Point. Однако согласно другим источникам, эти чипы могут производиться с использованием ещё более передового техпроцесса N4X, лучше работающего с высокими тактовыми частотами.

Источник изображения: HardwareLuxx.de В самом кристалле CCD процессоров Ryzen 9000 присутствуют 8,315 млрд транзисторов, что является значительным приростом по сравнению с 6,5 млрд транзисторов в составе восьмиядерного кристалла CCD Durango чипов Ryzen 7000 на архитектуре Zen 4. Примечательно, что несмотря на увеличившееся на 28 % количество транзисторов, площадь CCD Eldora на базе Zen 5 на 0,5 % меньше, чем площадь CCD Durango на Zen 4 — 70,6 мм2 против 71 мм2. Напомним, что CCD Durango на Zen 4 производится с применением 5-нм техпроцесса TSMC N5.

Источник изображения: HardwareLuxx.de Таким образом, общее количество транзисторов в составе флагманского 16-ядерного процессора Ryzen 9 9950X с двумя чиплетами CCD составляет 20,03 млрд. В свою очередь Ryzen 7 9700X с одним CCD содержит 11,715 млрд транзисторов. Samsung представила свой первый 3-нм процессор — Exynos W1000 для будущих смарт-часов

03.07.2024 [13:44],

Николай Хижняк

Компания Samsung представила Exynos W1000 — первый процессор, выпускающийся с использованием её фирменного 3-нм технологического процесса производства. Предполагается, что чип станет основной для новых смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс который состоится на следующей неделе.

Источник изображений: Samsung Samsung сообщила, что Exynos W1000 выполнен с использованием её 3-нм техпроцесса второго поколения (вероятно, SF3). В составе процессора имеются одно ядро Cortex-A78, четыре Cortex-A55, GPU Mali-G68 MP2, поддерживающий экраны с разрешением до 640 × 640 пикселей, а также 32 Гбайт встроенной памяти. По словам компании, новый чип обеспечивает в 2,7 раза более быстрый запуск приложений по сравнению с Exynos W930, а его многопоточная производительность в 3,7 раза выше, чем у предшественника. Для уменьшения размера чипа, повышения его производительности и энергоэффективности Samsung использовала много новых технологий в Exynos W1000. Например, в нём задействуется технология упаковки FOPLP (Fan-Out Panel Level Packaging) для повышения энергоэффективности и лучшего рассеивания тепла. Для оснащение процессора встроенной оперативной и постоянной памятью использовалась технология упаковки ePOP (Package-on-Package). Кроме того, в новом процессоре применяется технология SiP (System-in-Package), благодаря которой в него интегрирован модуль управления питанием (PMIC). Для Exynos W1000 заявляется поддержка технологии 2.5D Always on Display (AoD), которая обеспечивает более качественное отображение изображения и цветов в режиме постоянно включённого дисплея. Кроме того, чип поддерживает Bluetooth LE для передачи звука и энергоэффективную оперативную память стандарта LPDDR5. Для новинки также заявляется поддержка 4G LTE, Bluetooth, Wi-Fi b/g/n, GPS и NFC. Согласно предыдущим слухам и утечкам, Exynos W1000 станет основной для смарт-часов Galaxy Watch 7 и Galaxy Watch Ultra, анонс которых ожидается на следующей неделе. Отмечается, что благодаря новым технологиям в составе Exynos W1000 эти устройства Samsung смогут работать в течение 2–3 дней от одного заряда батареи. Google откажется от услуг Samsung и поручит производство чипов Tensor G5 компании TSMC

20.06.2024 [18:11],

Николай Хижняк

Компания Google с 2025 будет выпускать свои фирменные процессоры Tensor на мощностях TSMC, сообщают сразу несколько источников. Первое поколение чипов Tensor компания представила в 2021 году в серии смартфонов Pixel 6. С тех пор данные процессоры производились по заказу компанией Samsung.

Источник изображения: Google Как сообщается, десятое поколение смартфонов Pixel будут работать на чипах Tensor G5, которые будут производиться с применением 3-нм техпроцесса TSMC. Соглашение о сотрудничестве между двумя компаниями было подписано ещё в июле 2023 года, сообщают источники. Актуальный Tensor G3 производится с применением 4-нм техпроцесса Samsung. Процессор Tensor G4, который ляжет в основу смартфонов серии Pixel 9, всё ещё будет выпускаться компанией Samsung, а вот его преемник станет первым процессором Google для мобильных устройств, которые будет поручено выпускать тайваньской компании TSMC. Как сообщает Business Korea, переход на новый техпроцесс для Tensor G5 неизбежен, поскольку все основные конкуренты Google, включая Qualcomm и MediaTek, будут выпускать свои будущие процессоры на 3-нм техпроцессе. А та же Apple использует 3-нм техпроцесс для производства процессоров для iPhone 15 Pro с 2023 года. В том же отчёте южнокорейского издания говорится, что Samsung тем временем борется с проблемами производительности и энергоэффективности своего флагманского мобильного чипа Exynos 2500. Сообщается, что энергопотребление и тепловыделение чипа примерно на 10-20 % выше, чем у чипов, выпускаемых согласно 3-нм процессу TSMC. По мнению ведущего аналитика Мин-Чи Куо (Ming-Chi Kuo), по этой причине Samsung может отказаться от использования Exynos 2500 в составе будущей линейки смартфонов Galaxy S25 в пользу процессоров Qualcomm Snapdragon. TSMC уверена в запуске 2-нм техпроцесса в следующем году, а Samsung намерена ускорить освоение 1-нм технологии

28.05.2024 [23:18],

Николай Хижняк

Тайваньский контрактный производитель чипов TSMC рассказал о том, как идёт освоение 2-нм технологического процесса производства микросхем. Компания уверена в успехе новой технологии — она считает, что 2-нм техпроцесс привлечёт больше клиентов, чем 3-нм.

Источник изображения: Business Korea Выступая на технологическом форуме 23 мая, вице-президент TSMC Чжан Сяоган (Zhang Xiaogang) заявил, что «развитие 2-нм техпроцесса идёт гладко» и что «массовое производство чипов по нормам 2-нм должно стать возможным примерно в 2025 году, как и планировалось», пишет тайваньское издание Industrial and Commercial Times. Таким образом, заявление топ-менеджера TSMC опровергает ранее ходившие слухи о том, что массовое производство чипов на основе 2-нм техпроцесса из-за технических проблем начнётся не раньше 2026 года. Слухи о том, что TSMC откладывает запуск 2-нм техпроцесса возникли на фоне того, что этот техпроцесс предполагает переход к производству транзисторов с круговым затвором GAA (Gate-All-Around). Эта технология была представлена компанией Samsung в 2022 году, когда производитель анонсировал переход к массовому производству чипов с применением 3-нм техпроцесса. GAA позволяет снизить утечку тока в транзисторах, повысив тем самым энергоэффективность чипов в целом. По словам Чжана Сяогана, «выход годной продукции с применением технологии GAA достиг 90 % от целевого показателя». «Спрос на 2-нм техпроцесс превысит спрос на 3-нм и 5-нм техпроцессы», — в свою очередь выразил уверенность генеральный директор TSMC Вэй Чжэцзя (Wei Zhejia). Он добавил, что компания также планирует к концу года утроить производственные мощности для выпуска 3-нм продуктов, но даже в этом случае не сможет покрыть все заказы. Уверенность TSMC в успехе нового техпроцесса объясняется её сотрудничеством с Apple — самым крупным клиентом TSMC, на которого приходится до 25–30 процентов заказов. Ранее сообщалось, что операционный директор Джефф Уильямс (Jeff Williams) недавно посетил Тайвань для проведения переговоров с TSMC о перспективе выпуска ИИ-чипов. По данным издания Business Korea, компания Samsung планирует провести 12–13 июня в Кремниевой долине мероприятие Foundry and SAFE Forum, на котором, как ожидается, представит новую технологическую «дорожную карту» и сообщит о переносе старта массового производства чипов по нормам 1 нм с 2027 на 2026 год. TSMC запустит массовое производство по оптимизированному 3-нм техпроцессу N3P уже в этом году

16.05.2024 [22:06],

Сергей Сурабекянц

На традиционном весеннем технологическом симпозиуме TSMC представила обновлённую информацию о состоянии своих текущих и будущих 3-нм техпроцессов. Технология N3E применяется в серийном производстве с четвёртого квартала 2023 года, в этом году будет запущено массовое производство по техпроцессу N3P, который сохранит преемственность по технологической оснастке и средствам проектирования. Кроме того, N3P призван обеспечить снижение уровня брака при производстве чипов.

Источник изображения: TSMC TSMC сообщает о высоком уровне выхода годной продукции у 3-нм технологического процесса второго поколения N3E. По данным компании, плотность дефектов D0 в N3E находится на одном уровне с 5-нм техпроцессом N5. Это немалое достижение, учитывая дополнительные сложности, связанные с разработкой последнего, ещё более совершенного поколения технологии FinFET. Передовые клиенты TSMC, такие как Apple, только что выпустившая процессор M4, смогут относительно быстро воспользоваться преимуществами улучшенного технологического узла. Техпроцесс N3E представляет собой упрощённую версию N3B, в которой исключены некоторые уровни EUV и не используется двойное экспонирование. Это снижает себестоимость производства и увеличивает производительность, хотя за это приходится платить некоторым снижением плотности транзисторов. В отличие от оригинального N3B, чей производственный цикл будет относительно коротким, поскольку единственным его крупным заказчиком выступила Apple, N3E будет востребован широким кругом клиентов TSMC, в том числе многими крупнейшими разработчиками чипов. На сегодняшний день N3P завершил весь квалификационный цикл испытаний, по данным компании его показатели выхода годной продукции будут близки к N3E. Благодаря применению оптической усадки, техпроцесс N3P позволяет разработчикам процессоров либо увеличивать производительность на 4 % при тех же токах утечки, либо снижать энергопотребление на 9 % при тех же тактовых частотах. N3P также призван увеличить плотность транзисторов на 4 % для «смешанной» конструкции чипа, к которой TSMC относит процессоры, состоящие на 50 % из логических схем, на 30 % из SRAM и на 20 % из аналоговых схем. Поскольку N3P является дальнейшим развитием N3E, он совместим со своим предшественником с точки зрения IP-блоков, правил процессов, инструментов разработки и методологии электронного проектирования (EDA). TSMC ожидает, что к концу года на большей части производства будет использоваться N3P, так как он обеспечивает более высокую производительность при меньших затратах. Samsung расскажет о GAA-транзисторах третьего поколения для 2-нм чипов в июне

30.04.2024 [23:00],

Николай Хижняк

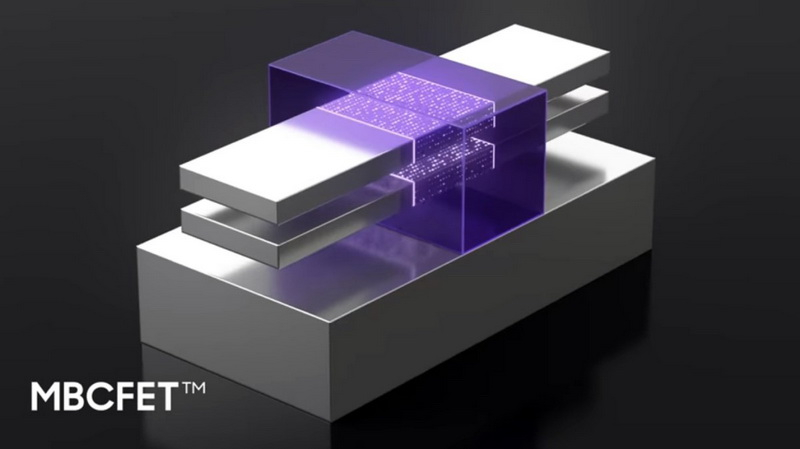

Компания Samsung разрабатывает транзисторы GAA (Gate-all-Around) нового поколения, которые будут применяться в чипах, производимых по её 2-нм техпроцессе. Компания планирует внедрить технологию в следующем году. Об этом сообщает южнокорейское издание Business Korea, ссылающееся на свои источники в отрасли.

Источник изображений: Samsung Со ссылкой на свои источники издание также отмечает, что Samsung собирается представить доклад о третьем поколении технологии GAA для своего 2-нм техпроцесса (SF2) в рамках конференции по вопросам полупроводниковых технологий VLSI Symposium 2024, которая будет проходить на Гавайях с 16 по 20 июня. Технология GAA, которую первой в мире поставила на коммерческие рельсы именно компания Samsung, это технология производства транзисторов с затвором, который полностью окружает канал. Поскольку с каждым переходом на новый техпроцесс транзисторы в составе полупроводника становятся меньше, контролировать движение тока в них становится всё сложнее. Однако GAA предлагает совершенно новую архитектуру транзистора, которая позволяет повысить его энергоэффективность. В настоящий момент Samsung является единственной компанией в мире, которая может массово применять технологию GAA-транзисторов для производства чипов. Она приступила к исследованию GAA ещё в начале 2000-х годов и впервые внедрила её для своего 3-нм техпроцесса в 2022 году. Однако из-за мировой экономической нестабильности, высокой стоимости производства, а также ограниченной клиентской базы в таких секторах, как мобильные устройства, спрос на 3-нм техпроцесс Samsung оказался несущественным. Как результат, лидерство в производстве 3-нм чипов перешло к тайваньскому контрактному производителю чипов TSMC, который использует более традиционные (и дешёвые) методы производства транзисторов. В ответ Samsung готовит второе поколение транзисторов GAA для 3-нм техпроцесса, которое она собирается представить в течение этого года. А в следующем году компания представит третье поколение GAA для 2-нм техпроцесса, чтобы закрепить лидерство в этом направлении. TSMC и Intel тоже планируют в конечном итоге перейти на использование технологии GAA с переходом на 2-нм техпроцесс производства, но случится это позже, чем у Samsung. Таким образом, у южнокорейской компании будет некое преимущество перед конкурентами. По крайней мере в теории. Официальное название технологии GAA от Samsung — MBCFET. Первое поколение GAA для техпроцесса 3 нм по сравнению с предыдущим поколением FinFET-транзисторов Samsung обеспечило 23-процентную прибавку в производительности, 16-процентное увеличение плотности и 45-процентное повышение энергоэффективности. Второе поколение GAA для 3 нм техпроцесса, как ожидается, обеспечит 30-процентную прибавку в производительности, 35-процентное повышение плотности, а также 50-процентное снижение в энергопотреблении. Что касается третьего поколения MBCFET, то для него также ожидается значительная прибавка в производительности с более чем 50-процентным повышением энергоэффективности по сравнению с предыдущим поколением технологии. TSMC научилась создавать монструозные двухэтажные процессоры размером с пластину

26.04.2024 [21:18],

Николай Хижняк

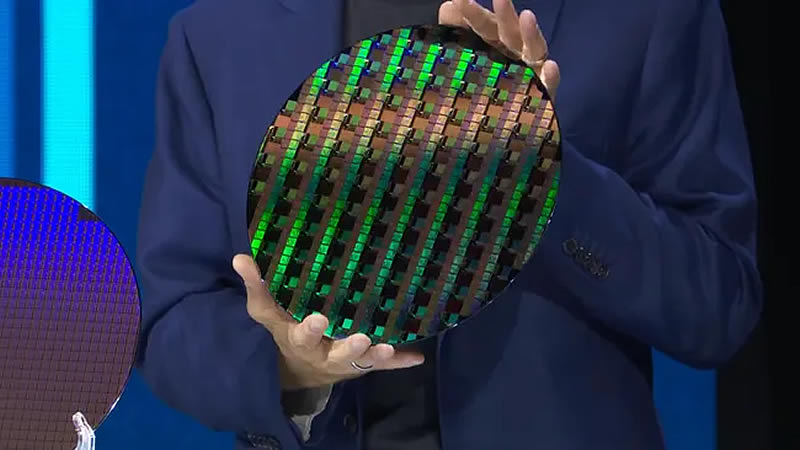

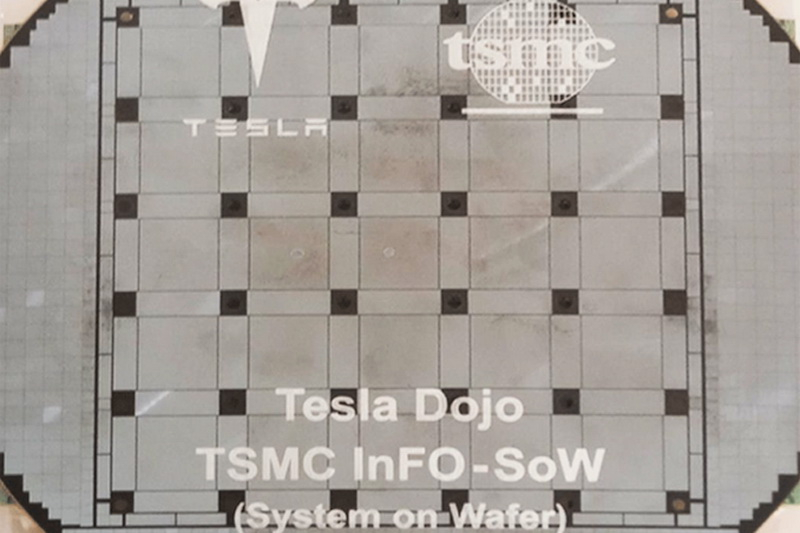

Компания TSMC представила новое поколение платформы «система-на-пластине» (System-On-Wafer) CoW-SoW, в которой применяется технология 3D-компоновки. Основой CoW-SoW является платформа InFO_SoW, представленная компанией в 2020 году, и позволяющая создавать логические процессоры в масштабе целой 300-мм кремниевой пластины. К настоящему моменту только компания Tesla адаптировала эту технологию. Она применяется в её суперкомпьютере Dojo.

Источник изображений: TSMC В новой платформе CoW-SoW компания TSMC собирается объединить два метода упаковки — InFO_SoW и System on Integrated Chips (SoIC). Благодаря использованию технологии Chip-on-Wafer (CoW) метод позволит размещать память и/или логику непосредственно поверх «системы на пластине». Ожидается, что новая технология CoW-SoW будет готова к массовому производству к 2027 году. «В будущем метод интеграции в масштабе пластины позволит нашим клиентам объединять ещё больше логических компонентов и памяти. Технология SoW — больше не фикция. Это то, над чем мы уже работаем с нашими клиентами для дальнейшей перспективы её использования в их существующих продуктах. Мы считаем, что передовая технология интеграции на уровне пластин предоставит нашим клиентам возможность продолжать наращивать вычислительные мощности их ИИ-систем или суперкомпьютеров», — сказал Кевин Чжан, вице-президент по развитию бизнеса в TSMC. Сейчас TSMC рассматривает возможность объединения в рамках платформы CoW-SoW логических процессоров с высокопроизводительной памятью HBM4. Последняя будет иметь 2048-битный интерфейс и располагаться непосредственно поверх логических микросхем. В то же время возможность размещения дополнительной логики на пластине позволила бы оптимизировать производственные издержки. Процессоры масштаба целой кремниевой пластины (например, WSE компании Cerebras), а также процессоры на платформе InFO_SoW обеспечивают значительные преимущества в вопросе производительности и эффективности за счёт высокой пропускной способности, низкой задержки в межъядерных связях, низкого сопротивления при передаче энергии и высокой энергоэффективности. В качестве дополнительного «бонуса» такие процессоры предлагают возможность размещения огромного количества вычислительных ядер. Однако у той же технологии InFO_SoW имеются и некоторые ограничения. Например, эффективность процессоров масштаба кремниевой пластины может ограничиваться эффективностью набортной памяти. Платформа CoW-SoW позволяет обойти это ограничение, поскольку в ней планируется применение высокопроизводительной памяти HBM4. В дополнение к этому обработка пластин InFO_SoW осуществляется с применением только одного технологического процесса, и он не поддерживает трёхмерную компоновку. Этот вопрос позволяет решить новая платформа CoW-SoW. |

|

✴ Входит в перечень общественных объединений и религиозных организаций, в отношении которых судом принято вступившее в законную силу решение о ликвидации или запрете деятельности по основаниям, предусмотренным Федеральным законом от 25.07.2002 № 114-ФЗ «О противодействии экстремистской деятельности»; |