⇣ Содержание

|

Опрос

|

реклама

Самое интересное в новостях

NAND/DRAM, почему стоим? или Микросхемы памяти у предела миниатюризации

Весной 2023-го южнокорейская Samsung Electronics с гордостью заявила о запуске в серийное производство первых в мире 16-Гбит чипов DDR5 DRAM, изготавливаемых по самой передовой на текущий момент технологии — относящейся к условному размерному классу «12 нм». Достижение? Да, но примерно в то же время на фабриках тайваньской TSMC вовсю разворачивался, пусть и не без затруднений, выпуск логических микросхем A17 и M3 по заказу Apple — с применением наиболее актуального на тот момент «3-нм» техпроцесса. Если учесть, что чипы полупроводниковой логики выпускались по нормам «10 нм» с 2017 г., а массовое освоение «7-нм» СБИС началось в 2018-м, просто-таки бросается в глаза существенный технологический зазор между микросхемами, ориентированными на хранение данных (в случае DRAM — временное, пока есть электрическое напряжение; для NAND — энергонезависимое), с одной стороны, и на логическую их обработку, с другой. Но почему так происходит и есть ли способ эффективно миниатюризировать DRAM (и, кстати, NAND тоже) ниже представляющегося каким-то зачарованным предела около «10 нм»? Ведь чем плотнее располагаются на микросхеме полупроводниковые ячейки, тем больший объём данных поместится на чип фиксированной площади. В плане оперативной памяти это особенно важно для таких требовательных к ней приложений, как генеративный ИИ, например, а о NAND и говорить не приходится — простора для хранения информации, как известно, много не бывает. Каждому ведь хочется иметь возможность запустить локальный мультимодальный чат-бот прямо на собственном смартфоне с парой десятков гигабайт ОЗУ на борту — и тут же сохранить на встроенном накопителе сгенерированное им по пользовательским подсказкам HD-видео, верно? ⇡#Капризная нанометрикаПолупроводниковое производство, в особенности по передовым технологическим нормам, — удовольствие чрезвычайно затратное, о чём мы не раз уже рассказывали в предыдущих материалах по этой теме. Однако после того, как технология на очередном уровне миниатюризации отлажена, себестоимость изготовления единичной пластины на данном фотолитографе стабилизируется — далее уже сравнительно слабо завися от того, какие именно полупроводниковые структуры формируют на очередной заготовке. И чем больше транзисторов удастся разместить на единице площади готового чипа, тем дешевле каждый из них обойдётся. Это принципиально важно именно с точки зрения массовости производства: доступные и более функциональные микросхемы очередного поколения будут приобретать охотнее — тем самым скорее выйдет окупить затраты на нынешние технологические линии и приступить к освоению следующих, что обеспечат изготовление ещё более миниатюрных транзисторов. Собственно, в отношении логических чипов, от простейших контроллеров ввода-вывода до многоядерных процессоров и сверхсложных систем-на-кристалле, эти соображения целиком и полностью справедливы. Но вот с микросхемами памяти, увы, возникает загвоздка: по определённому набору чисто физических причин они с огромным трудом поддаются дальнейшей миниатюризации. Ещё в ходе Intel Developer Forum 2003 года сами же организаторы этого мероприятия представили довольно пессимистичную презентацию, детально пояснив, почему память на ячейках NAND не будет производиться с применением техпроцессов миниатюрнее «60 нм», — и указав, какие дополнительные усилия корпорация предпримет для обхода этой досадной преграды на пути дальнейшего наращивания плотности записи данных для полупроводниковых накопителей без перехода к более мелкомасштабным производственным нормам.

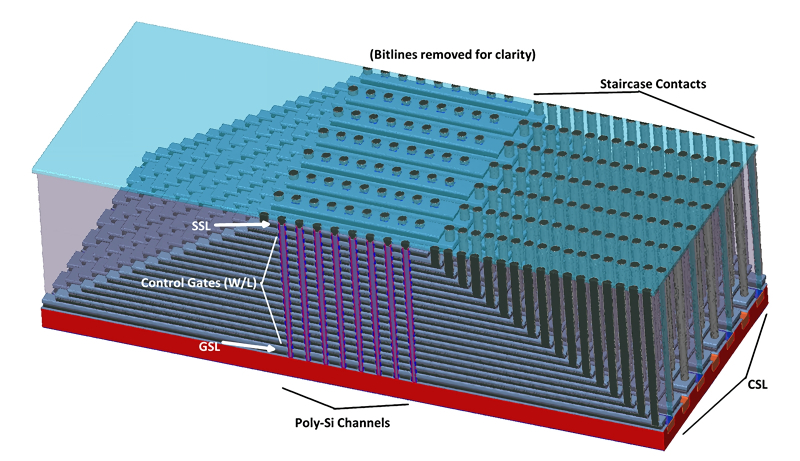

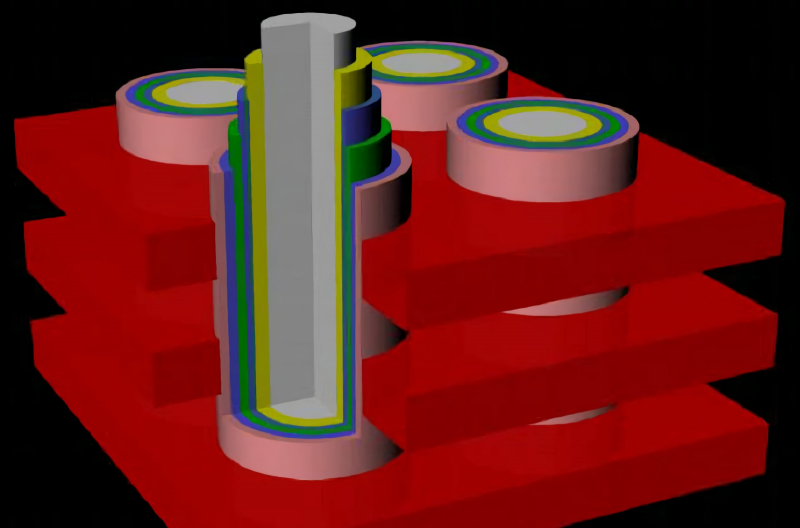

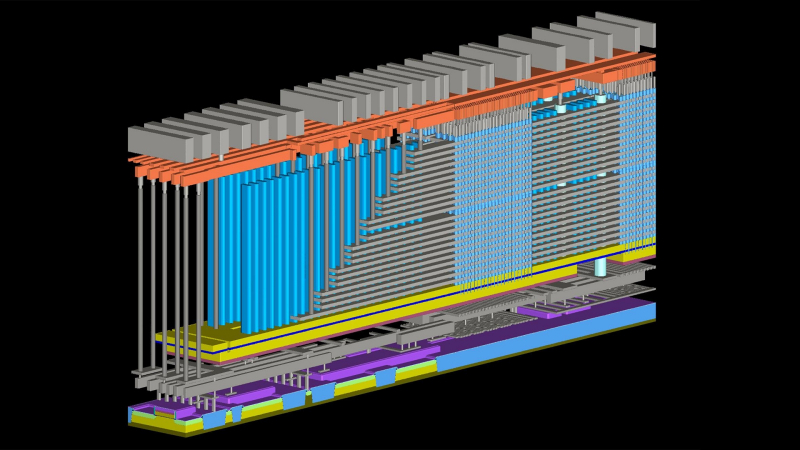

Общая схема организации чипа 3D NAND: собственно память — вертикальная структура в середине, пронизанная поликремниевыми каналами; ступенчатые конструкции по сторонам — подходящие к отдельным ячейкам каждого слоя контакты (источник: Techinsights) Правда, в соответствии с известной поговоркой о боящихся глазах и делающих руках, всего за десять лет с той поры сама Intel вполне успешно разработала и реализовала технологии изготовления NAND-памяти по «50-нм», «35-нм», «25-нм» и «20-нм» технологическим нормам. А в 2017-м самыми первыми СБИС, выполненными ею же по только что освоенному «10-нм» техпроцессу, стали как раз 64-слойные чипы 3D NAND, предназначенные для высокопроизводительных серверных накопителей. Вместе с тем в 2020-м наибольший объём микросхем 3D NAND в мире по-прежнему производился по техпроцессу «40 нм», обеспечивающему, как выяснилось эмпирическим путём, оптимальное соотношение между себестоимостью получаемого чипа и его ёмкостью. Значит, хотя в принципе технология получения «10-нм» чипов флеш-памяти сегодня уже доступна, ИТ-рынок с очевидностью выбирает чипы для хранения данных, созданные по формально вчетверо более крупномасштабным производственным нормам. В чём же тут дело? Если коротко, то в сознательной ориентации на такой технологический процесс, который был бы оптимальным с коммерческой точки зрения, а не абстрактно самым передовым. Миниатюризация же полупроводниковых ячеек памяти за порогом условных «40 нм» сопряжена с изрядными издержками.

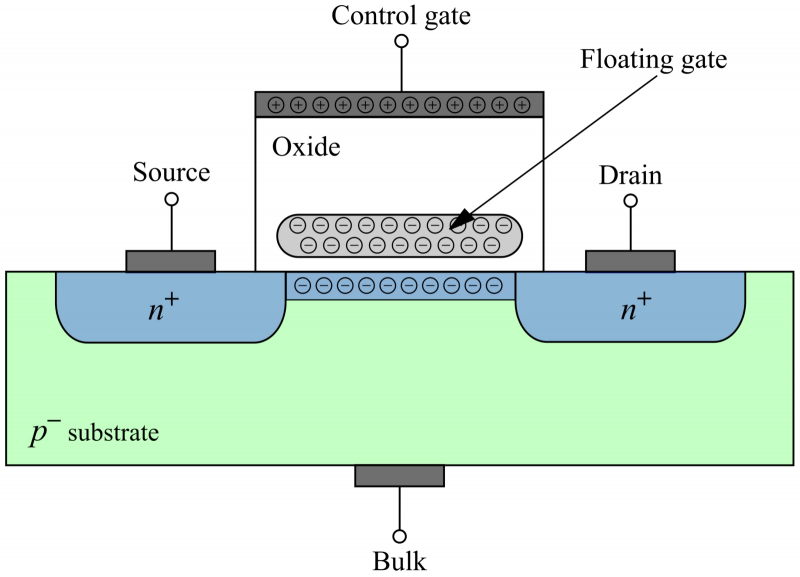

Планарный n-канальный МДП-транзистор с плавающим затвором: показаны исток и сток заряда, управляющий и собственно плавающий затворы (источник: All-Audio.pro) Исходный базовый элемент ячейки памяти NAND — n-канальный МДП-транзистор с плавающим затвором, конструкция которого позволяет заряду, однажды наведённому на этот самый плавающий затвор (гальванически изолированный от прочих структурных компонентов транзистора — оттого и «плавающий»), сохраняться очень долго, буквально годами, без дополнительного вмешательства. Это, собственно, и делает такие ячейки пригодными для построения энергонезависимой полупроводниковой памяти. Часто её не совсем корректно называют твердотельной, противопоставляя магнитным дисковым накопителям — можно подумать, у тех базовые структуры записи данных жидкие или газообразные! На деле же «твердотельный» — просто не самая удачная калька с англоязычного solid-state; ближе по смыслу, хотя и навряд ли лучше по звучанию, было бы «не содержащий подвижных частей», «механически инертный» или даже благолепно «несуетный». Изначально ячейки NAND располагались одна рядом с другой на плоскости, как и транзисторы в случае литографирования логических микросхем, — такой подход получил очевидное наименование планарного (planar), или 2D NAND. И уплотняли планарную полупроводниковую память точно таким же способом, что применялся для логических СБИС, — воспроизведением прежних структур с использованием всё новых, раз от раза более миниатюрных технологических процессов. Но поскольку на плавающих затворах внутри ячеек должен храниться электрический заряд, который, напомним, квантуется (его величина кратна элементарному единичному заряду электрона либо протона, т. е. фундаментальной физической постоянной), по мере приближения к определённому пределу миниатюрности размеров такого затвора всё сильнее проявляют себя квантовые эффекты.

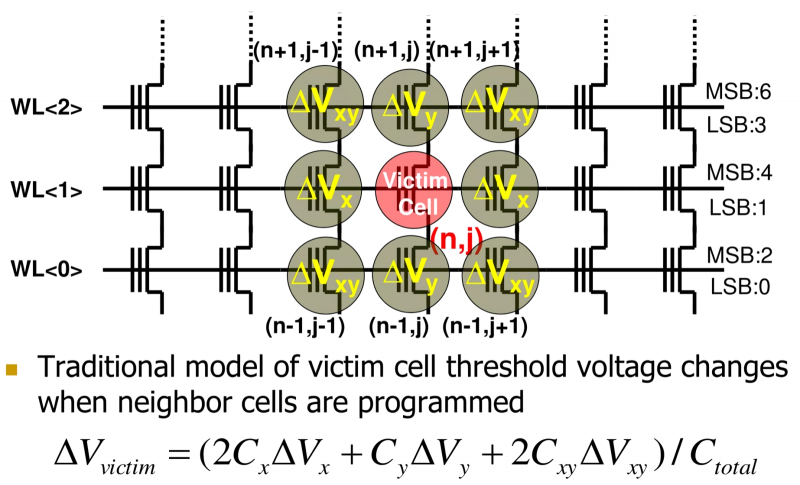

Пример программной межъячеечной интерференции: ячейка-«жертва» в центре испытывает паразитную наводку заряда в ходе изменения состояний соседних (источник: Carnegie Mellon University) Особенно критична с точки зрения надёжности сохранения данных утечка, или миграция, электрического заряда из данной ячейки в соседнюю, в том числе при записи данных. Программная межъячеечная интерференция (cell-to-cell program interference, паразитное изменение уровня заряда на плавающих затворах соседних NAND-ячеек в момент записи информации в намеченную — как раз вследствие миграции заряженных частиц), на нижней границе «10-нм» производственной нормы становится настоящим бичом полупроводниковых носителей данных. Бороться с ней, конечно, возможно, в том числе и программными же средствами (непрерывной верификацией контрольных сумм, превентивным кешированием потенциально уязвимых ячеек, записью информации сразу целыми блоками опять-таки через DRAM-кеш и пр.), но само наличие этого эффекта снижает производительность сверхминиатюрных NAND-чипов и сокращает продолжительность их эксплуатации. Не стоит также забывать, что у наноразмерных полупроводниковых элементов имеется физический предел допустимого числа циклов перезаписи, при превышении которого ячейки с большой вероятностью теряют свои рабочие свойства, — 50-100 тыс. циклов для одноуровневых ячеек, 1 тыс. и даже менее для трёхуровневых. А значит, делать их конструкцию ещё более уязвимой к утечкам заряда вследствие сокращения физических габаритов основных элементов транзистора — не самая блестящая инженерная идея. Оговорим здесь, кстати, не вдаваясь в технические детали, что на одном и том же плавающем затворе, не меняя технологии производства, можно хранить не 1 бит информации (есть заряд — логический ноль, нет — единица; на первый взгляд нелогично, но с прикладной инженерной точки зрения так удобнее), а несколько — в зависимости от конкретной величины заряда. Одноуровневые ячейки (single level cells, SLC) исходно были единственно доступной разновидностью NAND, но сегодня их применяют в основном лишь для создания промышленных полупроводниковых накопителей, для которых важнейшая характеристика — это надёжность при длительной эксплуатации, а цена за бит размещаемых на устройстве данных второстепенна и даже третьестепенна. В наиболее же широко распространённых SSD и картах памяти как потребительского, так и корпоративного класса довольно быстро начали применять сперва двухуровневые (MLC), затем трёхуровневые (3-bit MLC или TLC), четырёхуровневые (QLC) ячейки, а в перспективе маячат и пятиуровневые (PLC) NAND, — всё ради сокращения себестоимости хранения того самого единичного бита данных. Понятно, что для уверенного разделения даже пары бит, записанных на одном и том же плавающем затворе, требуется — на уровне проводимых внутренним контроллером устройства измерений — хорошо различать четыре градации заряда: для состояний «00», «01», «10» и «11». Иными словами, предельная величина заряда, с гарантией обеспечивающая надёжное хранение сразу двух бит данных, обязана быть достаточно высокой, — что уж говорить о ячейках TLC (8 градаций), QLC (16) и тем более PLC (32)! Межъячеечная интерференция при соответствующих высоких величинах подаваемых при операциях стирания/записи напряжений практически неизбежна, если расстояния между ячейками слишком малы. Вот почему массовая память 3D NAND уже в 2020 г., когда ячейки MLC успели потерять актуальность, а на смену TLC начинали приходить QLC, по сути застряла на рубеже «40 нм»: дальнейшая миниатюризация потребует изрядных инвестиций в НИОКР по новым материалам для формирования различных элементов сохраняющих данные транзисторов. ⇡#Когда приходится мелочитьсяЧто именно подразумевается под словом «застряла», наглядно поясняет на страницах своего блога Джим Хэнди (Jim Handy), известный в полупроводниковой индустрии независимый аналитик, успевший поработать в National Semiconductor, Intel и Siemens, а также входящий в консультативный совет Flash Memory Summit. 3D NAND, как наверняка уже ясно читателям материала о выходе чипов в третье измерение, в первом приближении состоит из сложенных стопочкой планарных блоков ячеек, прошитых не просто транспортными (для передачи электрического заряда), но логически функциональными межсоединениями. Собственно, те каналы — «штольни», «колодцы», — что пронизывают чередующиеся слои «полупроводник—диэлектрик», и представляют собой основу для формирования хранящих электрический заряд ячеек на каждом из уровней. Вот почему у инженеров крайне узок круг возможностей для поступательной миниатюризации NAND-чипов — и этот момент имеет смысл разъяснить чуть подробнее.

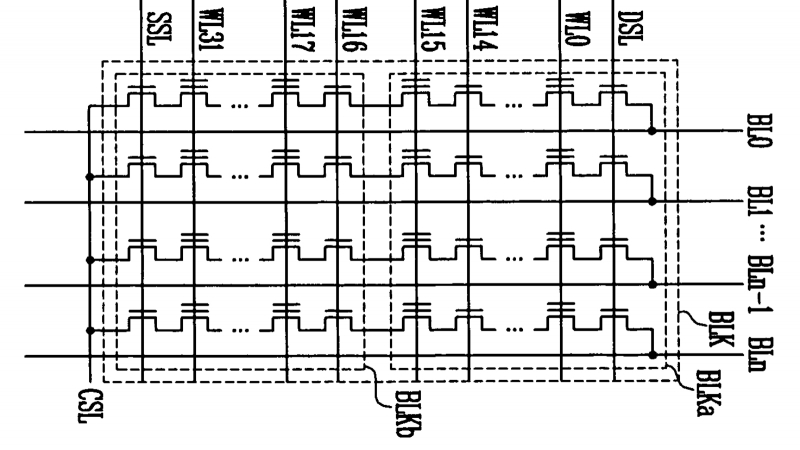

Поликремниевые шины WL (worldlines) соединяют управляющие затворы планарных ячеек NAND (источник: The Memory Guy) Базовый, классический на сегодня способ промышленной (пригодной для тиражирования в больших объёмах на фотолитографических станках) вертикальной укладки флеш-ячеек был предложен Toshiba в 2007 г.: он представляет собой вполне логичное развитие классической компоновки ячеек 2D NAND. В этой компоновке контрольные (не плавающие, а как раз те, что управляют сохраняемыми на них уровнями заряда) затворы каждой ячейки памяти соединяются «по столбцам» токоведущими шинами из поликристаллического кремния, легированного определёнными присадками. При переходе к 3D NAND вместо этих линейных шин за соединение контрольных затворов групп ячеек отвечают уже плоские слои поликристаллического кремния. И выстраивается вся трёхмерная структура будущей микросхемы памяти в несколько проходов, последовательно. Первым делом на кремниевой подложке стандартными методами фотолитографии формируют логические контрольные элементы будущих микросхем флеш-памяти — её базовый, управляющий слой. Там же размещаются токоведущие дорожки для связи между собой будущих вертикальных межсоединений. Всё это покрывается слоем изолятора (оксида всё того же кремния), поверх которого осаждается проводящий слой поликристаллического кремния — а уже на нём, собственно, формируются контрольные затворы будущих ячеек памяти первого слоя. Далее изолятор и поликремний чередуются — столько раз, сколько позволяет технология (в настоящее время Samsung работает над 280-слойной QLC 3D NAND, и даже материковая китайская YMTC самостоятельно освоила, невзирая на драконовские рестрикции Минторга США, 232-слойную память), — после чего весь получившийся слоистый пирог прошивают методом протравливания почти насквозь, до кремниевого основания, круглыми в сечении вертикальными шурфами-колодцами. Эта же технология, кстати, ещё раньше начала применяться при создании многослойных микросхем оперативной памяти (DRAM trench cell), так что долго её осваивать чипмейкерам не пришлось.

Схематическая демонстрация внутренней структуры шурфов 3D NAND: разными цветами показаны различные по химическому составу компоненты (источник: SanDisk) Главное достоинство описанного способа — в том, что весь набор вертикальных шурфов, в которых затем разместятся электрически активные «струны» (strings), выполняют лишь за один проход, что требует применения единственной фотомаски и последующей процедуры протравливания, — сколько бы слоёв проводника и изолятора ни было предварительно образовано. Правда, сами колодцы приходится делать достаточно широкими, поскольку пустыми они не останутся: их внутренняя структура, собственно, и будет формировать в каждом из слоёв ячейки хранения заряда, — за исключением лишь контрольных затворов, которыми выступают прилежащие к границам шурфов участки поликристаллического кремния. Как же получить внутри колодца необходимые для работы транзисторов-накопителей каналы и плавающие затворы? Всё довольно прозрачно: с применением отлично освоенного полупроводниковыми инженерами метода химического осаждения из паровой фазы (chemical vapor deposition, CVD) нужно последовательно изнутри поместить на стенки вертикальных колодцев слои изолятора (оксид кремния), материала собственно плавающего затвора (нитрид кремния), ещё одного изолятора, потом проводника — поликристаллического кремния — и, наконец, заполнить оставшийся узкий шурф опять-таки изолятором. Иногда поликремний занимает всё оставшееся пространство внутри колодца, и центральный ствол из изолятора не формируют, — это зависит от особенностей конкретного технологического процесса. В любом случае затем требуется ещё один цикл фотолитографии с маскированием и последующим травлением — чтобы размежевать вертикальные «струны», на которые оказываются таким образом нанизанными группы NAND-ячеек.

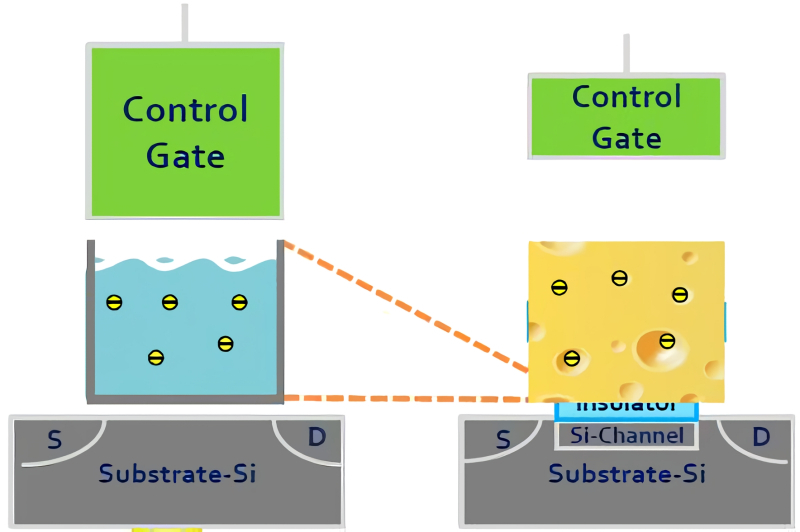

Образное представление отличия ячейки CTF (справа) от транзистора с плавающим затвором: в последнем электроны в составе этого затвора движутся относительно свободно и потому могут легко «расплескаться», как вода из чашки, под внешним воздействием; в CTF же заряженные частицы ведут себя словно пузырьки воздуха в швейцарском сыре — степень их свободы существенно ограничена (источник: Samsung) Если уж говорить совсем строго, то структура, в которой поликристаллический кремний (с определёнными добавками, разумеется) играет роль постоянного хранителя заряда, не может называться «МДП-транзистором с плавающим затвором», хотя принцип её действия по сути тот же самый. Это так называемая флеш-память с ловушкой заряда (charge trap flash, CTF): главная особенность её в том, что сберегающий заряд элемент (упомянутый ранее нитрид кремния) здесь — диэлектрик, а вовсе не полупроводник, как в случае плавающего затвора. С точки зрения многослойной конструкции 3D NAND это просто находка: расположенные поблизости — на соседних участках вертикальной «струны» — диэлектрики, логически относящиеся к разным транзисторам, но физически представляющие собой части единой структуры, куда менее склонны обмениваться зарядами (порождать утечки), чем полупроводники. В результате отпадает сама необходимость каким-то образом разграничивать при производстве содержимое колодцев по слоям, — что неимоверно упрощает и удешевляет изготовление трёхмерной памяти по сравнению с ситуацией, когда она строилась бы именно на классических транзисторах с плавающим затвором. Ещё одна безусловная выгода зарядовой ловушки — в том, что для записи заряда определённой величины в неё требуется меньшее напряжение, чем в случае транзистора с плавающим затвором, что ощутимо снижает «скорость выгорания» ячейки памяти в процессе многократной перезаписи. Так или иначе, минимальный диаметр шурфа в чипах 3D NAND — и, следовательно, максимальное число размещаемых на единице площади каждого слоя полупроводниковых ячеек с плавающим затвором — определяется той предельно допустимой толщиной, при которой расположенные внутри колодца слои продолжают исполнять свои функции. Точный нижний предел составляет здесь, очевидно, один атом (молекулу) — это в том случае, если удастся отыскать материалы, сохраняющие необходимые для работы МДП-транзистора свойства в одноатомном/одномолекулярном слое. Но по состоянию на 2020 г. из чисто экономических соображений — если учесть простоту получения и дешевизну широко применяемых в полупроводниковой литографии материалов — оказалось, что «40-нм» техпроцесс, который позволяет оперировать соответствующими толщинами в многие десятки и сотни атомов для каждого слоя, для массового поточного изготовления многослойной флеш-памяти оптимален.

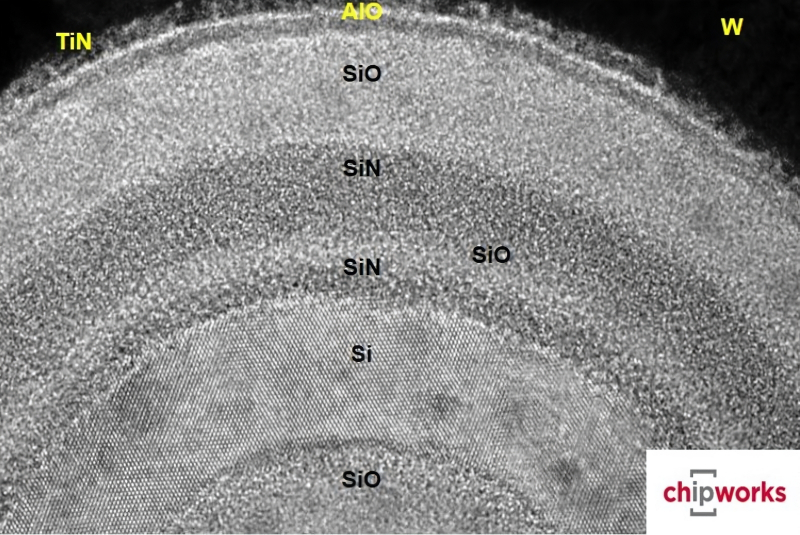

Микроскопическое изображение поперечного среза «струны» в составе чипа 3D NAND разработки Intel и Micron 2015 г.: во втором от центра слое, кремниевом (Si), явственно видна кристаллическая структура укладки отдельных атомов (источник: ChipWorks) В то время, когда совершался переход от 64- и 96-слойных 3D NAND к 128- и 176-слойным, типичное отношение длины к ширине (диаметру) каждого из протравливаемых в условно 100-слойной заготовке шурфов составляло около 60:1. Это соответствует — по пропорциям — полутораметровой в длину водопроводной трубе дюймового калибра. Причём следует помнить, что такой колодец приходится не микро-, а уже наноскопическими методами выстилать изнутри нужными материалами в несколько слоёв с величайшей тщательностью и равномерностью — задача с инженерной точки зрения сложная, но вполне уверенно решаемая. Сегодня активно производят 218- и 230-слойные чипы 3D NAND, а в 2024-2025-м можно ожидать появления 321-слойных, а затем и 430-слойных. Правда, здесь применяются технологии двойной, а в перспективе и тройной укладки микросхем (double-stack, triple-stack architecture) на манер используемого для логических СБИС подхода direct hybrid bonding, когда два-три крупных многослойных блока соединяются сверхскоростными, но очень короткими промежуточными шинами: скажем, 232-слойная NAND разработки Micron представляет собой «сэндвич» из пары 116-слойных чиплетов. ⇡#Только 3DПримерно к 2009 г. мировая индустрия NAND уверенно освоила изготовление планарных микросхем памяти по «45-нм» техпроцессу. Уже одно это позволило радикально снизить удельную розничную цену за условный 1 Гбайт ёмкости SSD с 40 долл. США, характерных для 2007 г., до примерно 2,5 долл. (HDD потребительского класса, к слову, в то время обходились примерно в 9 центов за 1 Гбайт, но это к теме настоящей статьи не относится). Наиболее передовым фотолитографическим инструментом были тогда машины на аргонфторидных лазерах с рабочей длиной волны 193 нм, которые путём целого ряда ухищрений (в частности, применения погружной оптики с численной апертурой 1,35) на самом пределе возможностей сумели достичь фактического разрешения 38 нм. Соответственно, далее миниатюризировать производственные нормы для планарных микросхем NAND, сохраняя технологию прежней, было уже невозможно.

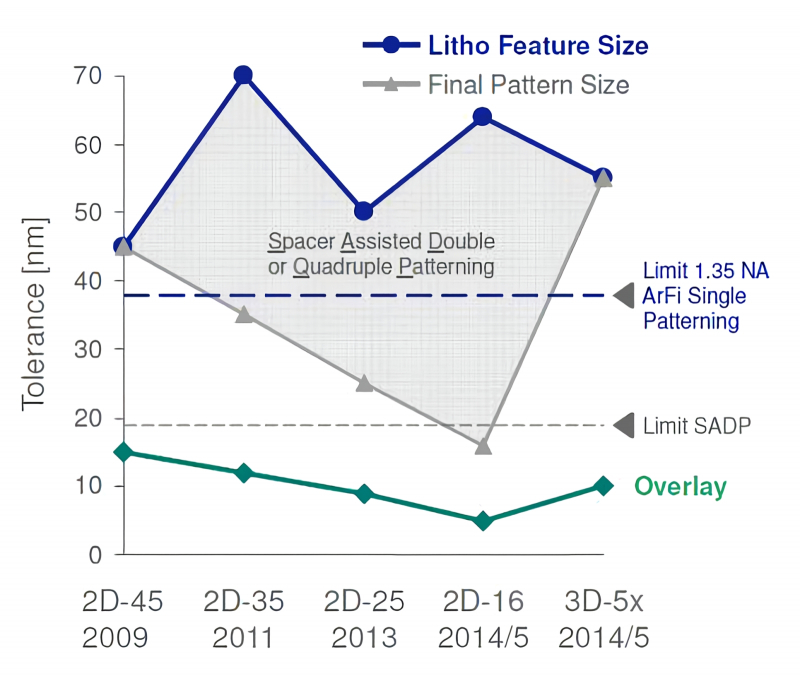

Изменения «номиналов» производственных процессов для 2D и 3D NAND до 2014/2015 гг. (зелёная линия), соответствующие фактические технологические нормы фотолитографов (синяя линия) и потенциал их сокращения за счёт SADP/SAQP (серая линия); см. также пояснения в тексте (источник: ASML) Зато через пару лет, в 2011-м, чипмейкеры в массовом порядке принялись применять при выпуске флеш-памяти двухпроходную фотолитографию (SADP), отлично зарекомендовавшую себя в ходе изготовления логических СБИС. Таким образом, заявленные как «35-нм» чипы 2D NAND 2011 г. выпуска на деле производились по прекрасно отлаженному и заведомо недорогому техпроцессу «70 нм» — но уже в два приёма. В 2013-м поставщики чипов памяти перешли на «50-нм» фотолитографы, что при использовании всё того же SADP позволило им ничтоже сумняшеся выпускать «25-нм» планарную NAND-память. А вот в 2014-2015 гг. гранды полупроводниковой индустрии, желая и далее снижать удельную себестоимость 1 Гбайт флеш-памяти, двинулись двумя параллельными путями. Первый предполагал сохранение планарной компоновки NAND и переход от SADP к SAQP, четырёхпроходной литографии, — это давало возможность освоить на номинально «65-нм» машинах выпуск «16-нм» микросхем. Безусловное преимущество здесь — возможность эксплуатировать не просто недорогое, а уже многократно окупившее себя за прежние годы оборудование. Серьёзный недостаток — значительный рост издержек из-за снижения выхода годной продукции по мере увеличения числа тонких сверхпрецизионных операций в производственном цикле. Второй же путь предусматривал переход к как раз доведённой к тому времени до ума технологии 3D NAND — с моментальным отказом от многопроходной фотолитографии, что сразу же повышало долю годной продукции в общем выходе, и с задействованием чуть более передового, но всё равно на тот момент прекрасно отлаженного «55-нм» техпроцесса. При этом число транзисторов на единицу площади чипа не то что не сокращалось, а за счёт многослойности СБИС, наоборот, резко увеличивалось, — даже с учётом почти четырёхкратного отката в номинальной разрешающей способности: с «16 нм» до «55 нм». Не случайно Toshiba, одной из первых решившаяся на массовое внедрение 3D NAND, во внутренних документах называла эту технологию BiCS — акронимом фразы Bit Cost Scaling, «масштабирование цены единичного бита». Здоровая тяга бизнесменов к максимальному снижению издержек в очередной раз сделалась двигателем прогресса. Разработанная примерно тогда же, к 2013 г., Samsung и Hynix альтернативная BiCS технология 3D NAND делает ставку на металлические затворы вместо поликремниевых и отличается по ряду других конструктивных особенностей, но общий принцип действия там тот же.

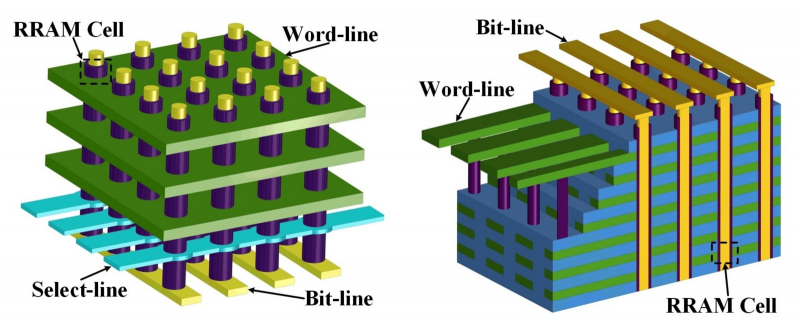

Трёхмерная вертикальная резистивная память со случайным доступом (это не тавтология, она так и называется — three-dimensional vertical resistive random access memory, 3D VRRAM), одна из перспективных разработок для организации подсистемы памяти в нейроморфных компьютерах, по принципу построения очень напоминает структуру BiCS — 3D NAND (источник: Micromachines) Впрочем, одним только созданием многослойного блока ячеек, предназначенных для хранения заряда, дело не ограничивается. Надо ещё позаботиться о том, чтобы подвести к контрольным затворам каждой из них управляющие шины. Но как это сделать, если предназначенная для чтения/записи логика должна располагаться на плоскости, а структура NAND-слоёв трёхмерна? Выход был найден вполне логичный: шурфы для формирования ячеек памяти протравливают лишь в срединной части каждой будущей микросхемы, оставляя по сторонам достаточный зазор, чтобы на финальном этапе создать — также методом последовательного травления, но уже со сдвигом маски — структуру ступенчатой террасы. А затем к открытым проводящим участкам каждого слоя присоединяются управляющие шины — снова по уже знакомой читателям наших материалов схеме: заполнение всего удалённого объёма диэлектриком — протравливание шурфов до каждого нужного слоя — создание в этих шурфах канала проводимости из поликристаллического кремния либо вольфрама — формирование верхнего слоя чипа, на котором выводы получившихся контрольных шин соединяются нужным образом. Кстати, в 2023 г. уже все NAND-чипмейкеры, как отмечают эксперты отрасли, перешли к обособленному (от создания ячеек собственно памяти) изготовлению управляющих контуров для них. Безусловно, технология 3D NAND не свободна от недостатков: по состоянию на 2017 г., скажем, для 32-слойной памяти Samsung эффективная площадь одной ячейки (не столбца в 32 слоя высотой, а именно одной, с учётом общего их числа в микросхеме стандартных габаритов) оценивалась в 31 тыс. кв. нм, тогда как для планарной, выполненной по «15-нм» техпроцессу, — в 30 раз меньше. Высокие и узкие стопки транзисторов на подложке флеш-чипа с ростом «этажности» теряют механическую прочность, становясь более подверженными повреждениям даже от сильной вибрации. Террасная структура подводимых к слоям контактов объедает немалую часть общей площади готовой микросхемы, так что если у 2D NAND около 65% всей её проекции приходится на ячейки памяти, то у 3D NAND — лишь около 40%. На первых этапах развития трёхмерной флеш-памяти её производителям приходилось затрачивать на необходимое оборудование и разработку новых технологических процессов (включая многослойную фотолитографию, при которой нарушение в любом из десятков слоёв приводит к выбраковке всей соответствующей микросхемы) в 3-5 раз больше средств, чем если бы они вложились в «14-16 нм» станки для изготовления передовой на тот момент планарной NAND и т. п.

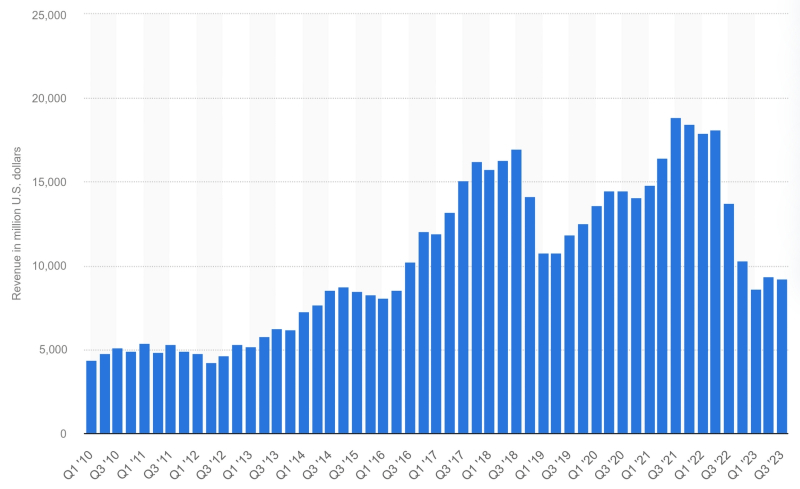

Совокупный объём мирового рынка памяти NAND в млн долл. США (в имперской нотации; запятая для отделения трёх десятичных порядков вместо точки) по кварталам: два внушительных провала после 2018 г. обусловлены не снижением спроса на флеш-память, а её удешевлением из-за перепроизводства в ответ на чрезмерно высокий в моменте спрос, — и чипмейкеры неплохо переносят эти спады выручки как раз благодаря неуклонному сокращению себестоимости всё более многослойных СБИС (источник: Statista) Непрерывные инвестиции в совершенствование флеш-технологий имеют вполне практический коммерческий смысл: по свидетельству Марка Уэбба (Mark Webb), ведущего аналитика MKW Ventures Consulting, с каждым очередным поколением чипы 3D NAND прибавляют от 30 до 50% слоёв по сравнению с предыдущим — при этом себестоимость их изготовления увеличивается лишь на 10-15%. В итоге за последние несколько лет суммарный объём флеш-памяти, выходящей из ворот чипмейкерских фабрик по всему миру, возрос на 30-35%. Выход в третье измерение уже позволил долгое время наращивать эффективный объём доступного хранилища данных на единицу занимаемой чипом площади, — и пока серьёзной альтернативы этому пути технологического развития не видно. Так, в 2021 г. представитель Samsung заявил на форуме IEEE IEDM, что к концу текущего десятилетия число слоёв в микросхемах 3D NAND достигнет тысячи. ⇡#Изнурительный бег на местеРазновидность технологии Samsung V-NAND (фирменный вариант 3D NAND), которая должна обеспечить в самом недалёком будущем выпуск чипов с тремя и более сотнями слоёв, станет уже девятым поколением данного производственного процесса — всего-то за десяток лет с той поры, когда трёхмерные флеш-ячейки массово пошли в серию. И это, как ожидается, тоже будет память «10-нм» класса — называемого так по традиции, восходящей ещё к 2013-2014 гг., когда новоявленную 24-слойную Samsung 3D V-NAND первого поколения представили как примерно соответствующую актуальным на тот момент планарным микросхемам памяти Toshiba номинальных производственных норм «15 нм», а также «16 нм» Micron, SK-Hynix и самой же Samsung. Официальный спикер южнокорейского чипмейкера на прямой вопрос о применённой для изготовления трёхмерной памяти технологии ответил уклончиво — что, мол, занимаемая готовым чипом площадь (die area) «приблизительно та же, что и у 2D NAND аналогичной ёмкости, выполненных по техпроцессу со средним для 10-нм шкалы размеров нормативом (mid-10nm-class)».

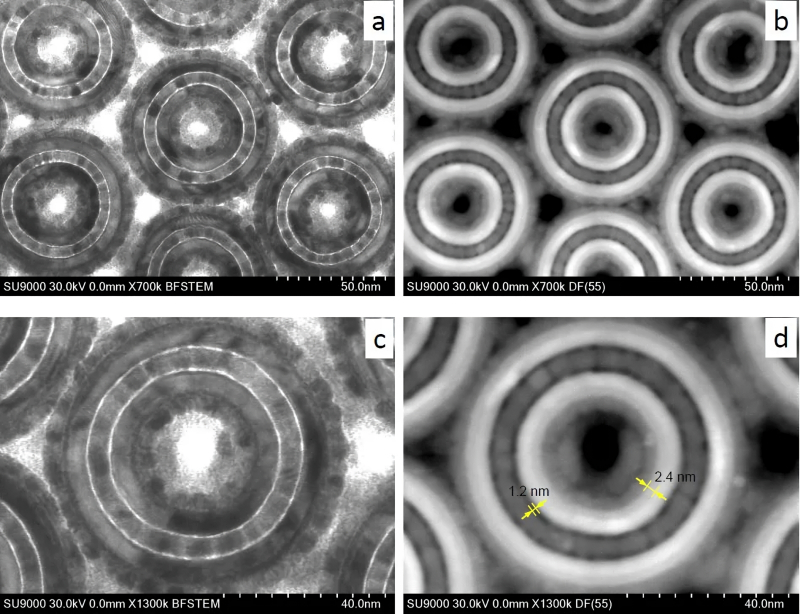

В начале 2023 г. Kioxia и Western Digital представили память BiCS 3D NAND 8-го поколения с 218 активными (содержащими ячейки собственно памяти) слоями (источник: Western Digital) Позже, как уже было отмечено выше, стало понятно, что речь идёт о «40-нм» производственной норме, но условное наименования «10 нм» или даже «1X нм» в отношении условной производственной нормы для массовых 3D NAND уже закрепилось. Соображения тут чисто математические: поскольку «15-16-нм» 2D-память была на тот момент уже трёхуровневой (три бита на ячейку), а трёхмерная первого поколения, 24-слойная, — одноуровневой, при равенстве объёмов двух чипов в битах 3D NAND должна содержать втрое больше транзисторов, распределённых по 24 слоям. Выходит, геометрическая плотность размещения NAND-ячеек в каждом слое трёхмерной памяти в 8 раз ниже, чем для 2D NAND. И поскольку площадь получается возведением длины в квадрат, линейный норматив размерности 3D NAND должен быть больше такового для планарной памяти в √8 раз — т. е. примерно в 2,8 раза. А 2,8 × «15» = «42», т. е. как раз те самые «40 нм». С оперативной памятью, DRAM, ситуация на вид даже более запутанная, хотя по сути тут всё значительно проще. Элементарная ячейка в данном случае образована конденсатором и транзистором (структурная схема one-transistor, one-capacitor — 1T1C) и потому способна чрезвычайно быстро забирать и отдавать электрический заряд. И, увы, конденсатор — необходимый для работы оперативной памяти компонент, а на нынешнем уровне развития полупроводниковых технологий существует физический запрет на использование техпроцесса миниатюрнее «10-нм» для массового изготовления таких элементов. С 2008 г. сокращение производственных норм было достаточно постепенным: сперва DRAM выполняли на фотолитографах стандарта «4x нм» (имеется в виду интервал от «49 нм» до «40 нм»), с 2010-го началось освоение класса размерности «3x», уже с 2011-го появились первые модули ОЗУ с микросхемами категории «2x», а в 2016-м чипмейкеры приступили к работе в области от «19 нм» и менее. Точнее, как раз на этом этапе начались первые по-настоящему серьёзные затруднения, и потому наименование «1x», или «10 nm Gen 1», получили технологии в интервале номинальных размерностей от «19 нм» до «17 нм». Затем логично были введены наименования «1y» (Gen 2; от «16 нм» до «14 нм»), «1z» (Gen 3; от «13 нм» до «11 нм»), «1a» (Gen 4), «1b» (Gen 5) и «1c» (Gen 6); впрочем, вместо латинских букв a, b и c могут использовать греческие — α, β, γ. То есть формально последние три разновидности техпроцессов всё равно остаются выше словно заговорённого предела «10 нм» — и в перспективе по меньшей мере ближайшего десятилетия инженеры и материаловеды со специализацией в полупроводниковой области не видят способов пересечь эту магическую черту. В чём же тут дело? Если говорить наиболее общо, то опять-таки в физике. Можно, конечно, предложить способ создания конденсатора, способного оперировать одним-единственным электроном (квантом электрического заряда), но пока нет измерительных устройств, способных замерять столь крохотные флуктуации электромагнитного поля для наноразмерных ячеек, размещённых на довольно небольших чипах, — да ещё и работающих в условиях значительного разогрева, т. е. с изрядным тепловым шумом. Иными словами, чтобы элементарная конденсаторная ячейка DRAM содержала измеримый имеющимися в распоряжении чипмейкеров (создателей контроллеров ОЗУ) заряд, она должна иметь довольно значительные физические габариты. Мало того, в идеале чем ближе её форма к квадратному в вертикальном сечении цилиндру — когда высота ячейки и диаметр её основания примерно равны, — тем лучше в конденсаторе удерживается заряд (и всё равно его приходится «освежать» раз в несколько десятков миллисекунд). Каждый миниатюрный конденсатор в ячейке DRAM представляет собой цилиндрическую структуру из металлического сердечника и оболочки, разделённых диэлектриком (metal-insulator-metal, MIM). Чем миниатюрнее техпроцесс, тем меньше габариты конденсатора — и уже при достижении производственной нормы «20 нм», как выяснилось в самом начале 2010-х, поступательно сокращать далее размеры ячейки DRAM попросту бессмысленно: заряд уверенно различимой (поверх всех сопутствующих шумов) величины она держать перестаёт. С этой напастью справились, предложив новые материалы для диэлектрика в составе MIM и новую схему размещения ячеек на поверхности полупроводникового кристалла — на манер пчелиных сот, что позволило увеличить физические размеры каждого конденсатора и тем самым сделать его более ёмким, не поступаясь ни миниатюрностью избранного техпроцесса, ни числом ячеек ОЗУ на чипе.

Поперечный срез массива конденсаторных ячеек DRAM под просвечивающим растровым электронным микроскопом с разными методами повышения контрастности. На кадре (d) отмечены слои с характерными толщинами 1,2 и 2,4 нм (источник: ST Instruments B.V.) Проникновение ещё глубже, в область «1x нм» и далее, стало для полупроводниковой индустрии настоящим вызовом, справляться с которым худо-бедно помогают такие знакомые нашим читателям методы, как переход от DUV- к EUV-фотолитографии, а также применение двух и четырёх проходов с последовательным уменьшением масштабов получаемых полупроводниковых структур вместо одного. Но бездушные законы физики неумолимы: оставаясь в рамках парадигмы 1T1C DRAM, преодолеть рубеж «10 нм» не удастся никак: величину заряда в MIM-конденсаторе не выйдет довести до уверенно измеримого уровня. Научно-инженерная мысль, конечно же, продолжает работать — в частности, предлагаются бесконденсаторные ячейки 1T DRAM на двухзатворных гребенчатых МОП-транзисторах с основой из поликристаллического кремния (polycrystalline-silicon dual-gate MOSFET with a fin-shaped structure), вертикальные полевые транзисторы (vertical field-effect transistors, VTFET) и другие сложносочинённые конструкции. В перспективе, не исключают эксперты, вместо DRAM выгоднее окажется использовать сверхскоростную память SRAM — как раз по той причине, что себестоимость тех и других модулей за рубежом «10 нм» уже не будет столь серьёзно различаться. Другими возможными вариантами замены DRAM могут стать память со сменой фазового состояния (phase-change memory, PCM), равно как и основанные на более классических для полупроводниковой индустрии принципах резистивная память с произвольным доступом (resistive random-access memory, ReRAM) или же память на эффекте передачи магнитного спинового момента (spin-transfer torque magnetic random-access memory, STT-MRAM). Но для развития каждого из этих направлений до стадии массового (и недорогого — по крайней мере сопоставимого с DRAM) производства необходимо приложить ещё немало усилий. И они, разумеется, будут приложены: слишком уж долго индустрия компьютерной памяти топчется у зачарованного порога «10 нм» — пора собраться с силами и его переступить! Если Вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

|